K4M56323LE - M(E)E/N/S/C/L/R

Mobile-SDRAM

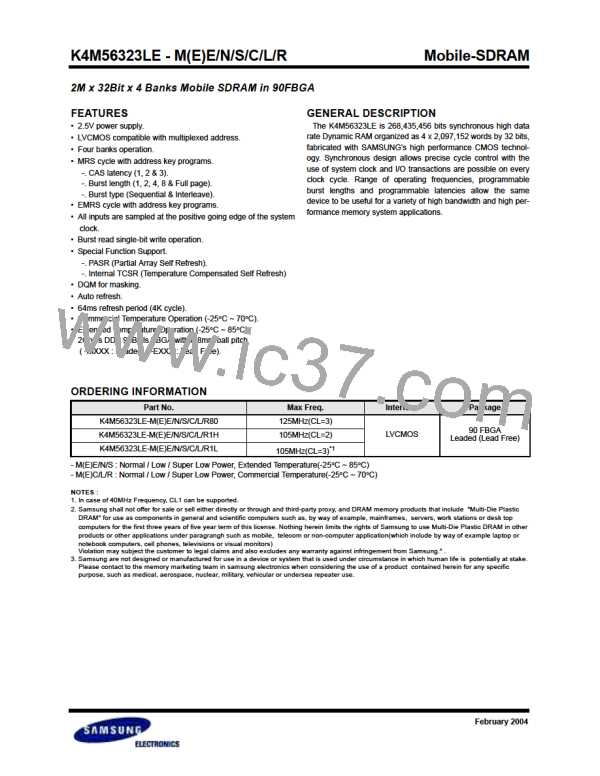

A. MODE REGISTER FIELD TABLE TO PROGRAM MODES

Register Programmed with Normal MRS

A9*2

BA0 ~ BA1

Address

A11 ~ A10/AP

A8

A7

A6

A5

A4

A3

A2

A1

A0

"0" Setting for

Normal MRS

RFU*1

Function

W.B.L

Test Mode

CAS Latency

BT

Burst Length

Normal MRS Mode

Test Mode

CAS Latency

Burst Type

Type

Burst Length

A8 A7

Type

Mode Register Set

Reserved

A6 A5 A4

Latency

Reserved

1

A3

0

A2

A1

0

A0

0

BT=0

BT=1

0

0

1

1

0

1

0

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

Sequential

Interleave

0

0

0

0

1

1

1

1

1

2

4

8

1

2

4

8

1

0

1

Reserved

2

Mode Select

1

0

Reserved

3

BA1 BA0

Mode

1

1

Write Burst Length

Length

Reserved

Reserved

Reserved

Reserved

0

0

Reserved Reserved

Reserved Reserved

Reserved Reserved

Full Page Reserved

Setting

for Nor-

mal MRS

A9

0

0

1

0

0

Burst

1

0

1

Single Bit

1

1

Full Page Length x32 : 256Mb(512)

Register Programmed with Extended MRS

Address

BA1

BA0

A11 ~ A10/AP

A9

RFU*1

A8

A7

A6

A5

A4

A3

A2

A1

A0

RFU*1

Function

Mode Select

DS

PASR

EMRS for PASR(Partial Array Self Ref.) & DS(Driver Strength)

Mode Select

Driver Strength

A5 Driver Strength

Full

PASR

BA1

BA0

Mode

A6

0

A2

A1

A0

# of Banks

4 Banks

0

0

1

1

0

1

0

1

Normal MRS

Reserved

0

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

1/2

2 Banks

EMRS for Mobile SDRAM

Reserved

1

Reserved

Reserved

1 Bank

1

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved Address

A11~A10/AP

0

A9

0

A8

0

A7

0

A4

0

A3

0

NOTES:

1. RFU(Reserved for future use) should stay "0" during MRS cycle.

2. If A9 is high during MRS cycle, "Burst Read Single Bit Write" function will be enabled.

February 2004

SAMSUNG [ SAMSUNG ]

SAMSUNG [ SAMSUNG ]