Rx5C348A/B

ꢀ Oscillation Halt Sensing, and Supply Voltage Monitoring

ꢁ

XSTP and VDET

The oscillation halt sensing circuit is configured to record a halt on oscillation by 32.768-kHz clock pulses. The

supply voltage monitoring circuit is configured to record a drop in supply voltage below a threshold voltage of 2.1

or 1.6v.

Each function has a monitor bit. I.e. XSTP bit is for the oscillation halt sensing circuit, and VDET is for the

supply voltage monitoring circuit. XSTP and VDET bits are activated to “H”. The XSTP and VDET accept only

the writing of 0. The XSTP bit is set to 1, when VDD power-up from 0V, but VDET is set to 0.

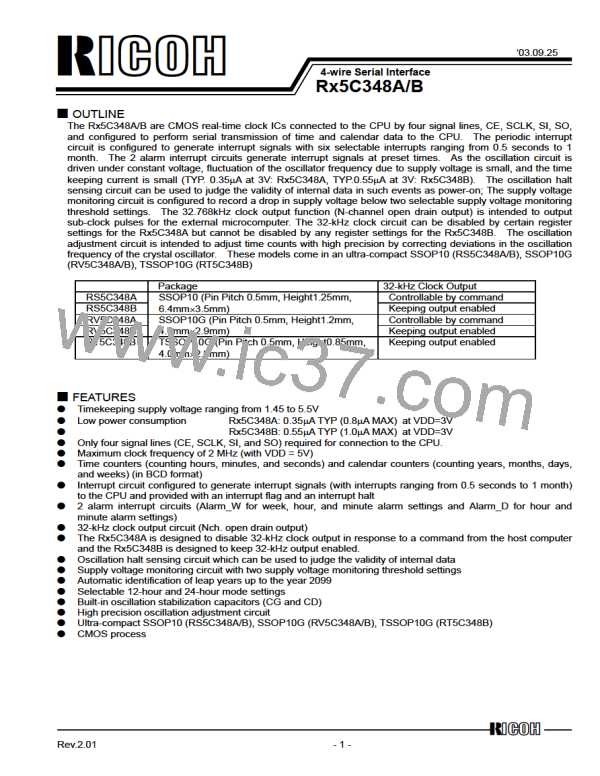

The functions of these two monitor bits are shown in the table below.

Oscillation Halt Sensing Circuit operates only when CE pin is Low. Sensing result is maintained after CE pin

changes from “L” to “H”.

XSTP

VDET

Conditions of supply voltage and oscillation

0

0

1

0

1

*

No drop in supply voltage below threshold voltage and no halt in oscillation

Drop in supply voltage below threshold voltage and no halt in oscillation

Halt on oscillation

Threshold voltage (2.1v or 1.6v)

VDD

32768Hz Oscillation

Oscillation halt

sensing flag (XSTP)

Supply voltage

monitor flag (VDET)

VDET←0

XSTP←0

VDET←0

VDET←0

XSTP←0

Internal initialization

period (1 to 2 sec.)

Internal initialization

period (1 to 2 sec.)

When the XSTP bit is set to 1 in the control register 2, the (0), F6 to F0, WALE, DALE, /12⋅24, /CLEN2, TEST,

CT2, CT1, CT0, VDSL, VDET, /CLEN1, CTFG, WAFG, DAFG, SCRATCH1/2/3 bits are reset to 0 in the oscillation

adjustment register, the control register 1, and the control register 2.

< Considerations in Using Oscillation Halt Sensing Circuit >

Be sure to prevent the oscillation halt sensing circuit from malfunctioning by preventing the following:

1) Instantaneous power-down on the VDD

2) Condensation on the crystal oscillator

3) On-board noise to the crystal oscillator

4) Applying to individual pins voltage exceeding their respective maximum ratings

In particular, note that the XSTP bit may fail to be set to 0 in the presence of any applied supply voltage as

illustrated below in such events as backup battery installation. Further, give special considerations to prevent

excessive chattering in the oscillation halt sensing circuit.

VDD

12345

Rev.2.01

- 32 -

RICOH [ RICOH ELECTRONICS DEVICES DIVISION ]

RICOH [ RICOH ELECTRONICS DEVICES DIVISION ]