455A Group

(6) Interrupt control registers

• Interrupt control register V2

The timer 3 interrupt enable bit are assigned to register V2. Set

the contents of this register through register A with the TV2A

instruction. The TAV2 instruction can be used to transfer the

contents of register V2 to register A.

• Interrupt control register V1

Interrupt enable bits of external 0, timer 1 and timer 2 are

assigned to register V1. Set the contents of this register through

register A with the TV1A instruction. The TAV1 instruction can

be used to transfer the contents of register V1 to register A.

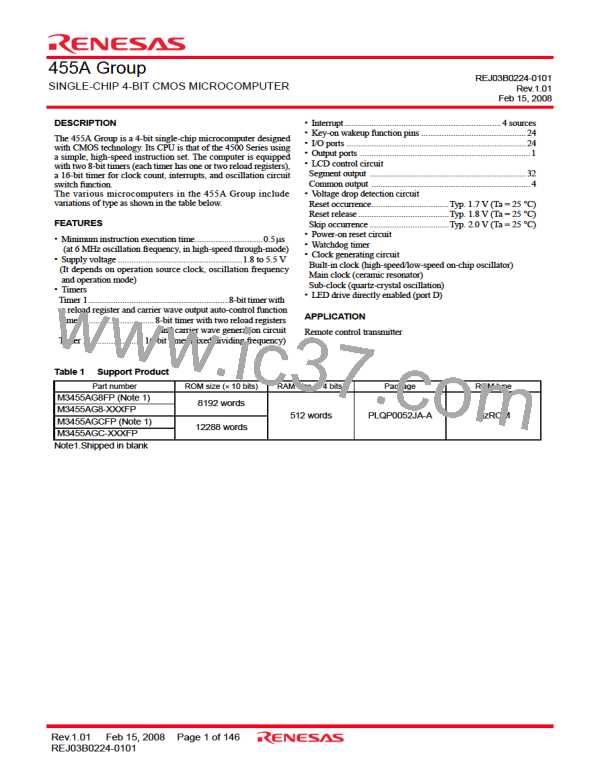

Table 13 Interrupt control registers

R/W

at power down : 00002

Interrupt control register V1

V13 Timer 2 interrupt enable bit

V12 Timer 1 interrupt enable bit

V11 Not used

at reset : 00002

TAV1/TV1A

0

1

0

1

0

1

0

1

Interrupt disabled (SNZT2 instruction is valid)

Interrupt enabled (SNZT2 instruction is invalid)

Interrupt disabled (SNZT1 instruction is valid)

Interrupt enabled (SNZT1 instruction is invalid)

This bit has no function, but read/write is enabled.

Interrupt disabled (SNZ0 instruction is valid)

Interrupt enabled (SNZ0 instruction is invalid)

V10 External 0 interrupt enable bit

R/W

TAV2/TV2A

Interrupt control register V2

V23 Not used

at reset : 00002

at power down : 00002

0

1

0

1

0

1

0

1

This bit has no function, but read/write is enabled.

This bit has no function, but read/write is enabled.

This bit has no function, but read/write is enabled.

V22 Not used

V21 Not used

Interrupt disabled (SNZT3 instruction is valid)

Interrupt enabled (SNZT3 instruction is invalid)

V20 Timer 3 interrupt enable bit

Note 1.“R” represents read enabled, and “W” represents write enabled.

(7) Interrupt sequence

Interrupts occur only when the respective INTE flag, interrupt

enable bits (V10, V12, V13, V30), and interrupt request flag are

set to “1.” The interrupt occurs two or three cycles after the cycle

where all the above three conditions are satisfied.

The interrupt occurs after three machine cycles if instructions

other than one-cycle instruction are executed when the

conditions are satisfied (Refer to Figure 27).

Rev.1.01 Feb 15, 2008 Page 25 of 146

REJ03B0224-0101

RENESAS [ RENESAS TECHNOLOGY CORP ]

RENESAS [ RENESAS TECHNOLOGY CORP ]