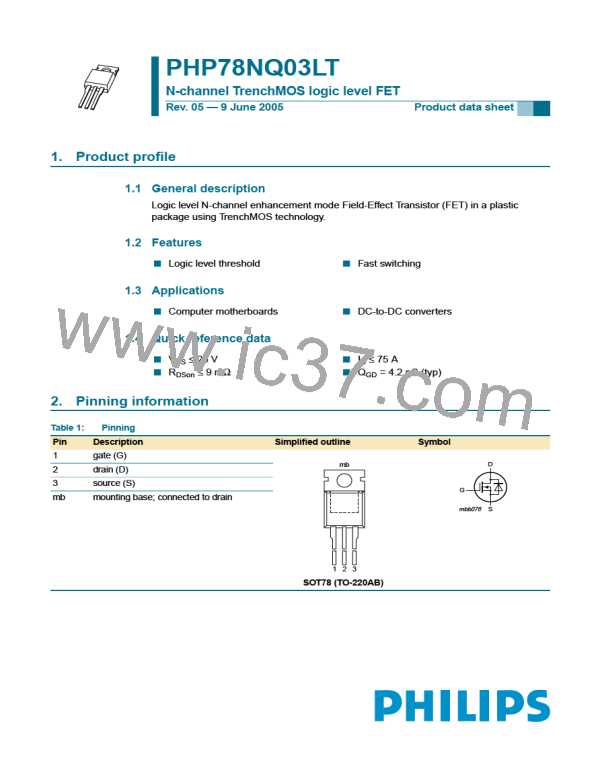

PHP78NQ03LT

Philips Semiconductors

N-channel TrenchMOS logic level FET

03aa16

03aa24

120

120

Ider

(%)

Pder

(%)

80

80

40

0

40

0

0

50

100

150

200

mb (°C)

0

50

100

150

200

Tmb ( C)

°

T

Ptot

ID

Pder

=

× 100%

Ider

=

× 100%

-----------------------

-------------------

P

I

°

°

tot(25 C)

D(25 C)

Fig 1. Normalized total power dissipation as a

function of mounting base temperature

Fig 2. Normalized continuous drain current as a

function of mounting base temperature

003aaa175

103

ID

Limit RDSon = VDS / ID

(A)

t = 10

p

s

µ

102

100

s

µ

DC

1 ms

10 ms

10

100 ms

1

1

10

102

VDS (V)

Tmb = 25 °C; IDM is single pulse; VGS = 5 V

Fig 3. Safe operating area; continuous and peak drain currents as a function of drain-source voltage

9397 750 15086

© Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet

Rev. 05 — 9 June 2005

3 of 12

NXP [ NXP ]

NXP [ NXP ]