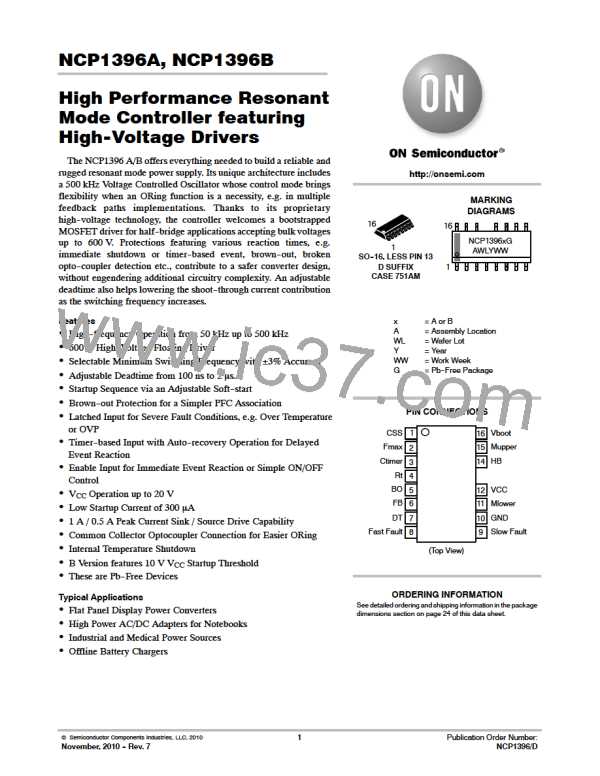

NCP1396A, NCP1396B

During the discharge time, the clock comparator is high

overthe VCOleadassoonasthe output voltage hasreached

the target. If not, then the minimum switching frequency is

reached and a fault is detected on the feedback pin

(typically below 600 mV). Figure 41 depicts a typical

frequency evolution with soft-start.

and un-validates the AND gates: both outputs are low.

When the comparator goes back to the low level, duringthe

timing capacitor Ct recharge time, A and B outputs are

validated. By connecting a resistor RDT to ground, it

creates a current whose image serves to discharge the Ct

capacitor: we control the dead-time. The typical range

evolves between 100 ns (RDT = 3.5 kΩ) and 2 ms (RDT =

83.5 kΩ). Figure 43 shows the typical waveforms.

Fsw

Fmax

Soft--start Sequence

If no FB

Action

In resonant controllers, a soft-start is needed to avoid

suddenly applying the full current into the resonating

circuit. In this controller, a soft-start capacitor connects to

pin 1 and offers a smooth frequency variation upon

start-up: when the circuit starts topulse, the VCO ispushed

to the maximum switching frequency imposed by pin 2.

Then, it linearly decreases its frequency toward the

minimum frequency selected by a resistor on pin 4. Of

course, practically, the feedback loop is suppose to take

Fmin

Vss

Soft--start Duration

Figure 41. Soft--start Behavior

20.0

10.0

0

Ires

--10.0

SS

Action

--20.0

177

Target is

175

Vout

Reached

173

171

169

1.00 m

1.40 m

1.80 m

200 m

600 m

time in seconds

Figure 42. A Typical Start--up Sequence on a LLC Converter

Please note that the soft-start will be activated in the

following conditions:

- A startup sequence

- During auto-recovery burst mode

- A brown-out recovery

- A temperature shutdown recovery

The fast fault input undergoes a special treatment. Since

we want to implement skip cycle through the fast fault

input on the NCP1396A, we cannot activate the soft-start

every time the feedback pin stops the operations in low

power mode. Therefore, when the fast fault pin is released,

no soft-start occurs to offer the best skip cycle behavior.

However, it is very possible to combine skip cycle and true

fast fault input, e.g. via ORing diodes driving pin 6. In that

case, if a signal maintains the fast fault input high long

enough to bring the feedback level down (that is to say

below 0.6 V) since the output voltage starts to fall down,

then the soft-start is activated after the release of the pin.

In the B version tailored to operate from an auxiliary 12 V

power supply, the soft-start is always activated upon the

fast fault input release, whatever the feedback condition is.

http://onsemi.com

18

ONSEMI [ ONSEMI ]

ONSEMI [ ONSEMI ]