CAT24C64

S

T

A

R

T

BUS ACTIVITY:

MASTER

S

T

ADDRESS

BYTE

ADDRESS

BYTE

DATA

BYTE

SLAVE

O

P

ADDRESS

a

15

− a

a

7

− a

d − d

7 0

8

0

S

P

* * *

A

C

K

A

C

K

A

C

K

A

C

K

SLAVE

*a − a are don’t care bits.

15

13

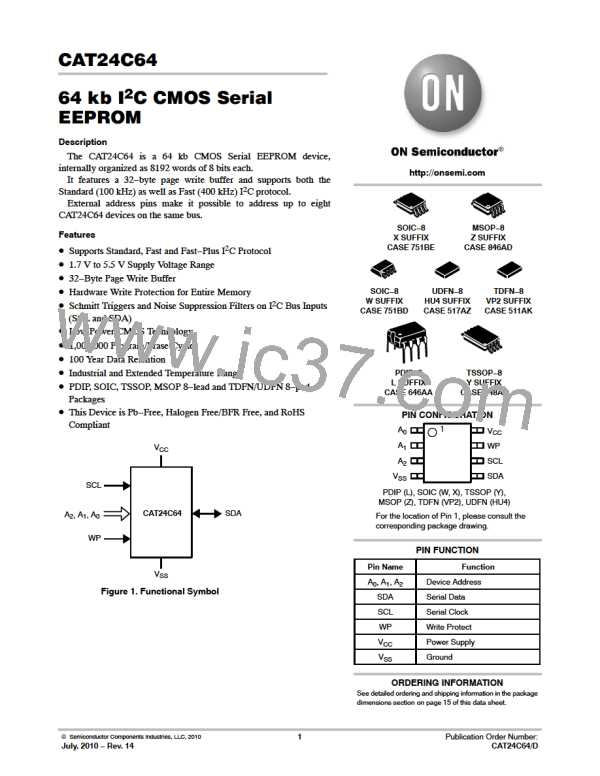

Figure 6. Byte Write Sequence

SCL

SDA

8th Bit

Byte n

ACK

t

WR

STOP

START

ADDRESS

CONDITION

CONDITION

Figure 7. Write Cycle Timing

BUS

ACTIVITY: S

T

A

S

T

DATA

BYTE

n

DATA

BYTE

n+1

DATA

BYTE

n+P

SLAVE

ADDRESS

ADDRESS

BYTE

ADDRESS

BYTE

MASTER

SLAVE

R

T

O

P

S

P

A

C

K

A

C

K

A

C

K

A

C

K

A

A

A

C

K

C

K

C

K

Figure 8. Page Write Sequence

ADDRESS

BYTE

DATA

BYTE

1

1

8

9

8

d

SCL

SDA

a

a

0

d

7

7

0

t

SU:WP

WP

t

HD:WP

Figure 9. WP Timing

http://onsemi.com

6

ONSEMI [ ONSEMI ]

ONSEMI [ ONSEMI ]