CAT24C64

BUS RELEASE DELAY (TRANSMITTER)

BUS RELEASE DELAY (RECEIVER)

SCL FROM

MASTER

1

8

9

DATA OUTPUT

FROM TRANSMITTER

DATA OUTPUT

FROM RECEIVER

ACK SETUP (≥ t

)

SU:DAT

START

ACK DELAY (≤ t

)

AA

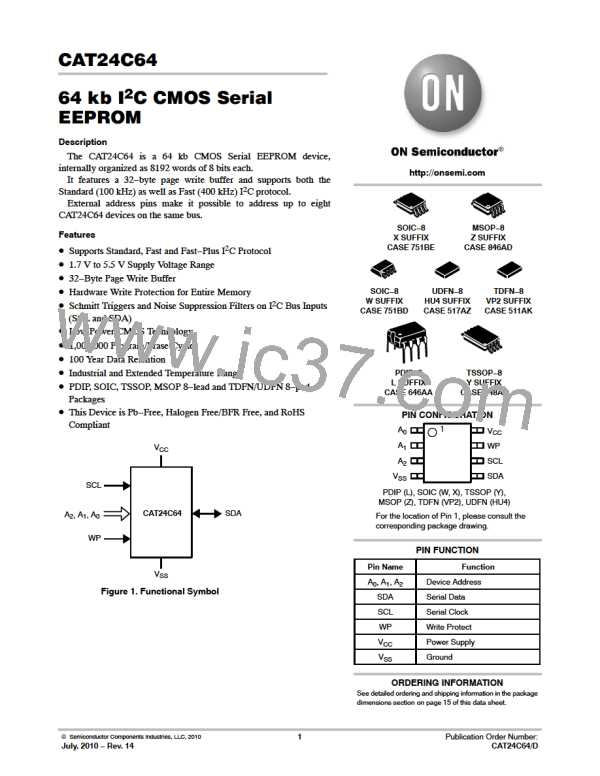

Figure 4. Acknowledge Timing

t

t

F

t

R

HIGH

t

t

LOW

LOW

SCL

t

t

HD:DAT

SU:STA

t

t

t

SU:DAT

SU:STO

HD:STA

SDA IN

t

BUF

t

AA

t

DH

SDA OUT

Figure 5. Bus Timing

WRITE OPERATIONS

Byte Write

Acknowledge Polling

To write data to memory, the Master creates a START

condition on the bus and then broadcasts a Slave address

with the R/W bit set to ‘0’. The Master then sends two

address bytes and a data byte and concludes the session by

creating a STOP condition on the bus. The Slave responds

with ACK after every byte sent by the Master (Figure 6). The

STOP starts the internal Write cycle, and while this

As soon (and as long) as internal Write is in progress, the

Slave will not acknowledge the Master. This feature enables

the Master to immediately follow-up with a new Read or

Write request, rather than wait for the maximum specified

Write time (t ) to elapse. Upon receiving a NoACK

WR

response from the Slave, the Master simply repeats the

request until the Slave responds with ACK.

operation is in progress (t ), the SDA output is tri-stated

and the Slave does not acknowledge the Master (Figure 7).

WR

Hardware Write Protection

With the WP pin held HIGH, the entire memory is

protected against Write operations. If the WP pin is left

floating or is grounded, it has no impact on the Write

operation. The state of the WP pin is strobed on the last

Page Write

The Byte Write operation can be expanded to Page Write,

by sending more than one data byte to the Slave before

issuing the STOP condition (Figure 8). Up to 32 (Note 10)

distinct data bytes can be loaded into the internal Page Write

Buffer starting at the address provided by the Master. The

page address is latched, and as long as the Master keeps

sending data, the internal byte address is incremented up to

the end of page, where it then wraps around (within the

page). New data can therefore replace data loaded earlier.

Following the STOP, data loaded during the Page Write

session will be written to memory in a single internal Write

st

falling edge of SCL immediately preceding the 1 data byte

(Figure 9). If the WP pin is HIGH during the strobe interval,

the Slave will not acknowledge the data byte and the Write

request will be rejected.

Delivery State

The CAT24C64 is shipped erased, i.e., all bytes are FFh.

10.CAT24C64 Rev. D (Not Recommended for New Designs)

has 64−Byte Page Write Buffer.

cycle (t ).

WR

http://onsemi.com

5

ONSEMI [ ONSEMI ]

ONSEMI [ ONSEMI ]