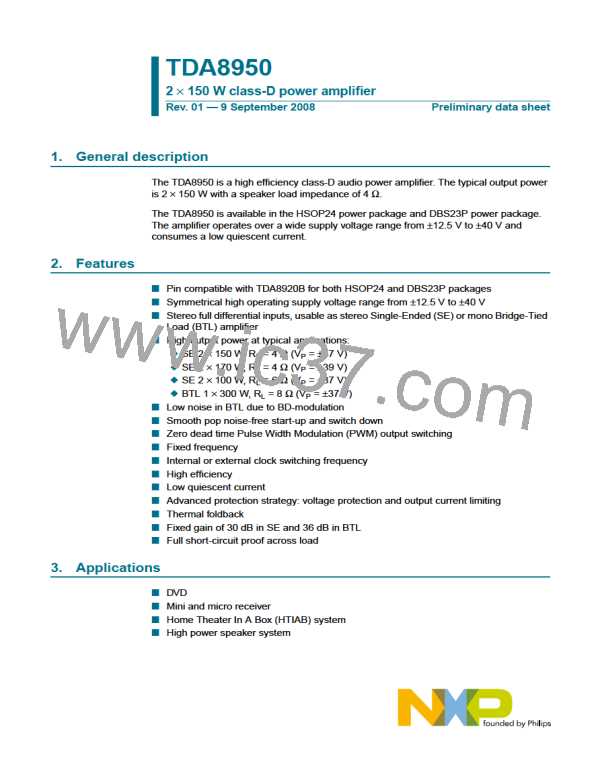

TDA8950

NXP Semiconductors

2 × 150 W class-D power amplifier

11. Static characteristics

Table 7.

Static characteristics

VP = ±35 V; fosc = 345 kHz; Tamb = 25 °C; unless otherwise specified.

Symbol

Supply

VP

Parameter

Conditions

Min

Typ

Max

Unit

[1]

supply voltage

±12.5 ±35

±40

90

V

VP(ovp)

VP(uvp)

Iq(tot)

overvoltage protection supply voltage non-operating; VDD − VSS

undervoltage protection supply voltage VDD − VSS

85

20

-

-

V

-

25

V

total quiescent current

Operating mode; no load; no

filter; no RC-snubber network

connected

50

75

mA

Istb

standby current

-

480

600

µA

Mode select input; pin MODE

[2]

[2][3]

[2][3]

[2][3]

VMODE

voltage on pin MODE

referenced to SGND

Standby mode

Mute mode

0

-

6.0

0.8

3.0

6.0

150

V

0

-

V

2.2

4.2

-

-

V

Operating mode

VI = 5.5 V

-

V

II

input current

110

µA

Audio inputs; pins IN1M, IN1P, IN2P and IN2M

VI input voltage

Amplifier outputs; pins OUT1 and OUT2

VO(offset) output offset voltage

[2]

DC input

-

0

-

V

SE; mute

-

-

-

-

-

-

-

-

±15

mV

mV

mV

mV

[4]

[4]

SE; operating

BTL; mute

±150

±21

BTL; operating

±210

Stabilizer output; pin STABI

VO(STABI)

output voltage on pin STABI

mute and operating; with

respect to VSSP1

9.3

9.8

10.3

V

Temperature protection

Tact(th_prot) thermal protection activation

temperature

-

-

154

153

-

-

°C

°C

[5]

Tact(th_fold) thermal foldback activation

temperature

closed loop SE voltage gain

reduced with 6 dB

[1] The circuit is DC adjusted at VP = ±12.5 V to ±42.5 V.

[2] With respect to SGND (0 V).

[3] The transition between Standby and Mute mode has hysteresis, while the slope of the transition between Mute and Operating mode is

determined by the time-constant of the RC-network on pin MODE; see Figure 8.

[4] DC output offset voltage is gradually applied to the output during the transition between the Mute and Operating modes. The slope

caused by any DC output offset is determined by the time-constant of the RC-network on pin MODE.

[5] At a junction temperature of approximately Tact(th_fold) − 5 °C the gain reduction will commence and at a junction temperature of

approximately Tact(th_prot) the amplifier switches off.

TDA8950_1

© NXP B.V. 2008. All rights reserved.

Preliminary data sheet

Rev. 01 — 9 September 2008

13 of 39

NXP [ NXP ]

NXP [ NXP ]