LPC546xx

NXP Semiconductors

32-bit ARM Cortex-M4 microcontroller

DDDꢀꢁꢂꢆꢃꢇꢇ

ꢂꢅꢇ

ꢊ$ꢌ0++]ꢋꢋ

ꢁꢆꢇ

ꢁꢅꢇ

ꢀꢆꢇ

ꢀꢅꢇ

ꢆꢇ

0ꢅꢉ65$0ꢉꢊ)52ꢍꢉ3//ꢋ

0ꢅꢉ65$0ꢉꢊ)52ꢋ

0ꢅꢉ)/$$6+ꢉꢊ)52ꢍꢉ3//ꢋ

0ꢅꢉ)/$$6+ꢉꢊ)52ꢋ

ꢀꢁ

ꢂꢃ

ꢄꢅ

ꢆꢇ

ꢀꢀꢄ

ꢀꢅꢁ

ꢀꢄꢃ

ꢀꢆꢅ

ꢁꢁꢇ

)UHTXHQF\ꢉꢊ0+]ꢋ

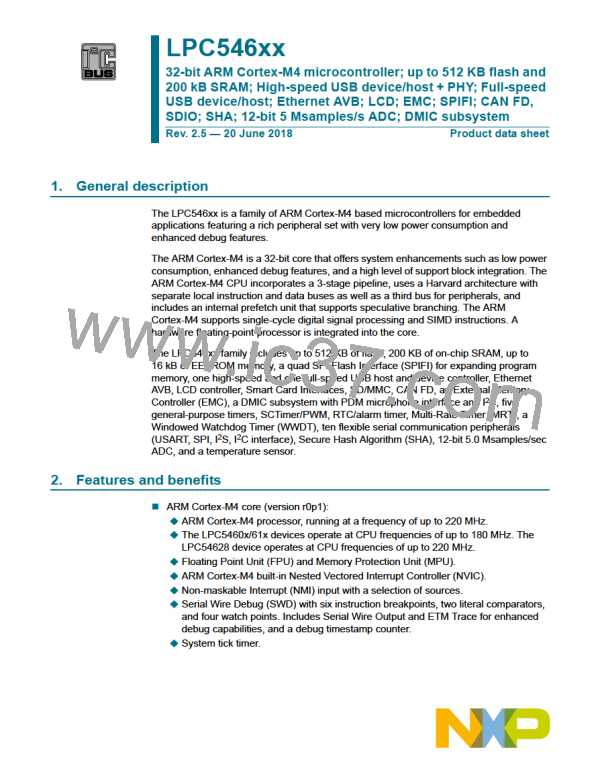

Conditions: VDD = 3.3 V; Tamb = 25 °C; active mode; all peripherals disabled; BOD disabled;

Acceleration enable bit in the FLASHCFG register is set to 0. See the FLASHCFG register in the

LPC546xx. User Manual for system clock flash access time settings. Measured with Keil uVision

v.5.21. Optimization level 0, optimized for time off. Coremark power consumption is based on the

power API library from the SDK software package available on nxp.com.

12 MHz, 24 MHz, 48 MHz, and 96 MHz: FRO enabled; PLL disabled.

36 MHz, 60 MHz, 72 MHz, 84 MHz, 108 MHz, 120 MHz, 132 MHz, 144 MHz, 156 MHz, 168 MHz,

180 MHz, 192 MHz, 204 MHz, 216 MHz, and 220 MHz: FRO enabled; PLL enabled.

CoreMark A/MHz from flash: SRAM1, SRAM2, SRAM3, and USB SRAM powered down. SRAM0

and SRAMX powered.

CoreMark A/MHz from SRAMX: SRAM0 is powered; flash is powered down.

Fig 15. CoreMark power consumption: typical A/MHz vs. frequency (MHz) from flash

and SRAMX

Table 16. Static characteristics: Power consumption in deep-sleep and deep power-down modes

Tamb = 40 C to +105 C, unless otherwise specified, 1.71 V VDD 2.7 V.

Symbol Parameter

Conditions

Min Typ[1][2] Max[3] Unit

IDD

supply current Deep-sleep mode; Flash is powered down

SRAMX (32 KB) powered

-

-

22

-

69

A

A

Tamb = 25 C

SRAMX (32 KB) powered

1150

Tamb = 105 C

Deep power-down mode

RTC oscillator input grounded (RTC oscillator

disabled)

-

-

-

326

-

1000

27

nA

A

nA

Tamb = 25 C

RTC oscillator input grounded (RTC oscillator

disabled)

Tamb = 105 C

RTC oscillator running with external crystal

VDD = VDDA = VREFP = VBAT = 1.8 V

340

-

[1] Typical ratings are not guaranteed. Typical values listed are at room temperature (25 C), VDD = 1.8 V.

[2] Characterized through bench measurements using typical samples.

LPC546xx

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

Product data sheet

Rev. 2.5 — 20 June 2018

91 of 169

NXP [ NXP ]

NXP [ NXP ]