Device operations

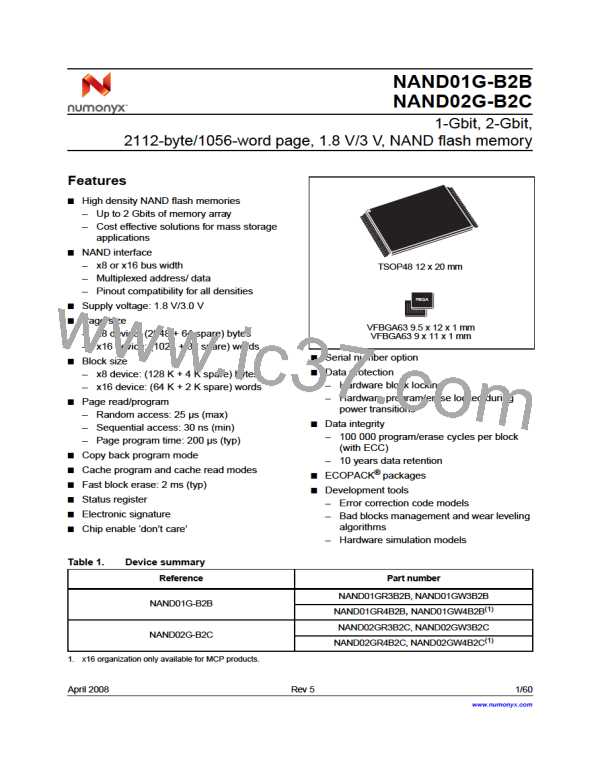

NAND01G-B2B, NAND02G-B2C

6.8

Read status register

The device contains a status register which provides information on the current or previous

program or erase operation. The various bits in the status register convey information and

errors on the operation.

The status register is read by issuing the Read Status Register command. The status

register information is present on the output data bus (I/O0-I/O7) on the falling edge of Chip

Enable or Read Enable, whichever occurs last. When several memories are connected in a

system, the use of Chip Enable and Read Enable signals allows the system to poll each

device separately, even when the Ready/Busy pins are common-wired. It is not necessary to

toggle the Chip Enable or Read Enable signals to update the contents of the status register.

After the Read Status Register command has been issued, the device remains in read

status register mode until another command is issued. Therefore if a Read Status Register

command is issued during a random read cycle a new Read command must be issued to

continue with a page read operation.

The Status Register bits are summarized in Table 13: Status register bits,. Refer to Table 13

in conjunction with the following text descriptions.

6.8.1

6.8.2

Write protection bit (SR7)

The write protection bit can be used to identify if the device is protected or not. If the write

protection bit is set to ‘1’ the device is not protected and program or erase operations are

allowed. If the write protection bit is set to ‘0’ the device is protected and program or erase

operations are not allowed.

P/E/R controller and cache ready/busy bit (SR6)

Status register bit SR6 has two different functions depending on the current operation.

During cache program operations SR6 acts as a cache program ready/busy bit, which

indicates whether the cache register is ready to accept new data. When SR6 is set to '0', the

cache register is busy and when SR6 is set to '1', the cache register is ready to accept new

data.

During all other operations SR6 acts as a P/E/R controller bit, which indicates whether the

P/E/R controller is active or inactive. When the P/E/R controller bit is set to ‘0’, the P/E/R

controller is active (device is busy); when the bit is set to ‘1’, the P/E/R controller is inactive

(device is ready).

6.8.3

P/E/R controller bit (SR5)

The program/erase/read controller bit indicates whether the P/E/R controller is active or

inactive. When the P/E/R controller bit is set to ‘0’, the P/E/R controller is active (device is

busy); when the bit is set to ‘1’, the P/E/R controller is inactive (device is ready).

30/60

NUMONYX [ NUMONYX B.V ]

NUMONYX [ NUMONYX B.V ]