NAND01G-B2B, NAND02G-B2C

Device operations

6.6

Block erase

Erase operations are done one block at a time. An erase operation sets all of the bits in the

addressed block to ‘1’. All previous data in the block is lost.

An erase operation consists of three steps (refer to Figure 14):

1. One bus cycle is required to setup the Block Erase command. Only addresses A18-

A28 (x8) or A17-A27 (x16) are used, the other address inputs are ignored

2. Two or three bus cycles are then required to load the address of the block to be erased.

Refer to Table 8 and Table 9 for the block addresses of each device

3. One bus cycle is required to issue the Block Erase Confirm command to start the P/E/R

controller.

The operation is initiated on the rising edge of write Enable, W, after the Confirm command

is issued. The P/E/R controller handles block erase and implements the verify process.

During the block erase operation, only the Read Status Register and Reset commands will

be accepted, all other commands will be ignored.

Once the program operation has completed the P/E/R controller bit SR6 is set to ‘1’ and the

Ready/Busy signal goes High. If the operation completed successfully, the write status bit

SR0 is ‘0’, otherwise it is set to ‘1’.

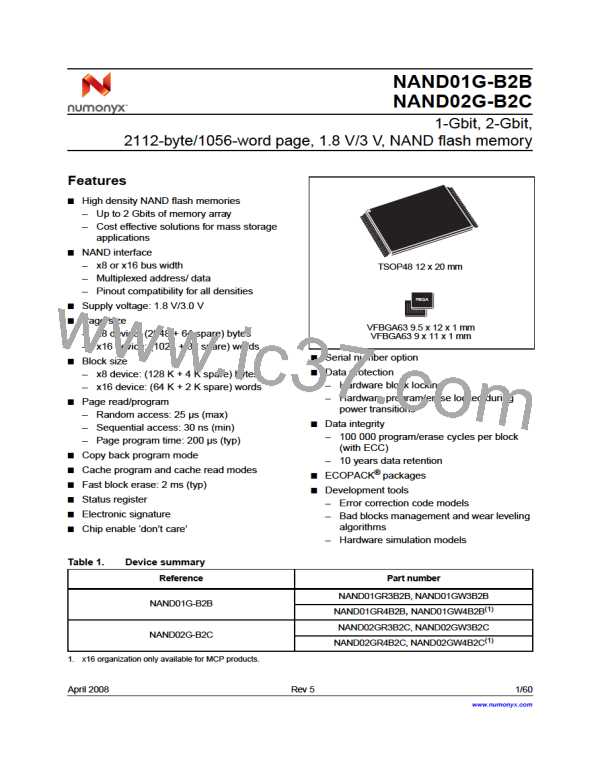

Figure 14. Block erase operation

tBLBH3

(Erase Busy time)

RB

Busy

Block Address

Inputs

I/O

60h

D0h

70h

SR0

Confirm

Code

Read Status Register

Block Erase

Setup Code

ai07593

6.7

Reset

The Reset command is used to reset the command interface and status register. If the

Reset command is issued during any operation, the operation will be aborted. If it was a

program or erase operation that was aborted, the contents of the memory locations being

modified will no longer be valid as the data will be partially programmed or erased.

If the device has already been reset then the new Reset command will not be accepted.

The Ready/Busy signal goes Low for t

after the Reset command is issued. The value

BLBH4

of t

depends on the operation that the device was performing when the command was

BLBH4

issued, refer to Table 25: AC characteristics for operations for the values.

29/60

NUMONYX [ NUMONYX B.V ]

NUMONYX [ NUMONYX B.V ]