Status Register

M29FxxxFT, M29FxxxFB

Table 10. Status Register Bits

Operation

Program

Address

DQ7

DQ7

DQ6

DQ5

DQ3

DQ2

RB

Any Address

Toggle

0

0

–

–

–

–

–

0

0

Program During

Erase Suspend

Any Address

DQ7

Toggle

Program Error

Chip Erase

Any Address

Any Address

Erasing Block

DQ7

Toggle

Toggle

Toggle

1

0

0

–

1

0

0

0

0

0

0

Toggle

Toggle

Block Erase before

timeout

No

Toggle

Non-Erasing Block

Erasing Block

0

0

0

Toggle

Toggle

Toggle

0

0

0

0

1

1

0

0

0

Toggle

Block Erase

No

Toggle

Non-Erasing Block

No

Toggle

Erasing Block

1

0

–

Toggle

1

1

0

Erase Suspend

Non-Erasing Block Data read as normal

Good Block

No

Toggle

0

Toggle

1

1

1

Address

Erase Error

Faulty Block

Address

0

Toggle

1

Toggle

0

Unspecified data bits should be ignored.

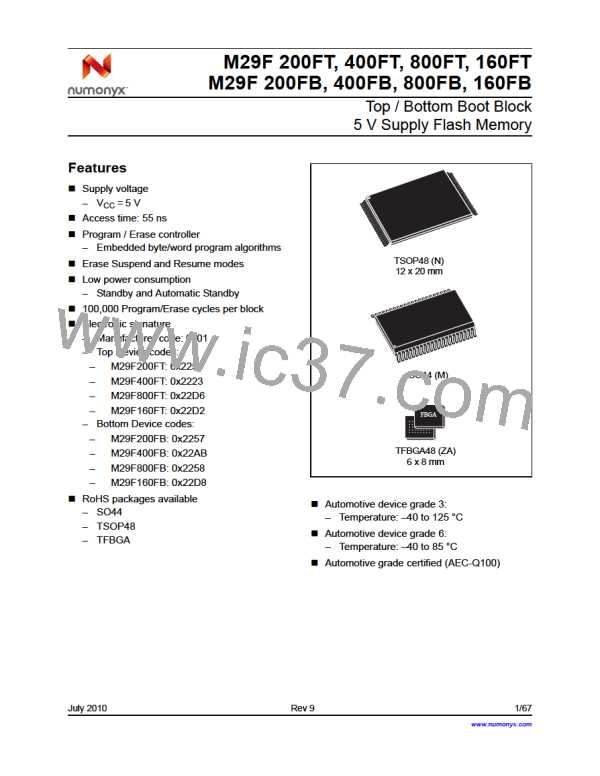

Figure 1. Data Polling Flowchart

START

READ DQ5 & DQ7

at VALID ADDRESS

DQ7

=

DATA

YES

NO

NO

DQ5

= 1

YES

READ DQ7

at VALID ADDRESS

DQ7

=

DATA

YES

NO

FAIL

PASS

AI03598

36/67

NUMONYX [ NUMONYX B.V ]

NUMONYX [ NUMONYX B.V ]