CHAPTER 4 CONFIGURATION EXAMPLES OF FPGA INTEGRATION

This chapter describes configuration examples in which the PCI host bridge macro is integrated in an FPGA

(Altera’s EP20K200EQC240-1X).

4.1 Conditions for Configuration Examples of FPGA Integration

The conditions in the configuration examples are as follows.

(1) CPU:

V850E/ME2

(2) Bus width of external bus interface: 32 bits

(3) CS space of PCI host bridge:

(4) CS space of SDRAM:

(5) SDRAM:

CSZ6

CSZ3

Connecting two 16 M × 16 SDRAMs (4 M × 16 × 4 banks)

(6) PCI connection:

2 devices

4.2 Points to Remember When Creating Top Layer of FPGA

Points to remember when integrating the PCI host bridge macro with an FPGA are indicated below.

(1) First decode the chip select from the address before creation.

• I_CPU_CS0_B: PCI host bridge register chip select

(Offset address in 3.4 Registers)

• I_CPU_CS1_B: PCI I/O area chip select

(See Figure 3-3 CPU Memory Space/PCI Bus I/O Space Address Map)

• I_CPU_CS2_B: PCI memory area chip select

(See Figure 3-4 CPU Memory Space/PCI Bus Memory Space Address Map)

(2) Because the buffers of the address bus and data bus for the expansion bus interface are output when the PCI

host bridge controls SDRAM, they become bidirectional pins via the selector.

The following pins that control SDRAM become 3-state output.

• DQM0 to DQM3, SDCKE, SDCS, SDRAS, SDCAS, SDWEZ

(3) The following PCI bus interface pins become bidirectional pins.

• AD, CBE, FRAME, IRDY, DEVSEL, TRDY, STOP, PAR, PERR

(4) There are three interrupt request output signals: one is output from the PCI host bridge; the remaining two are

INTA and INTB signals from the external PCI slot and are directly connected to the CPU.

57

Application Note U17121EJ1V1AN

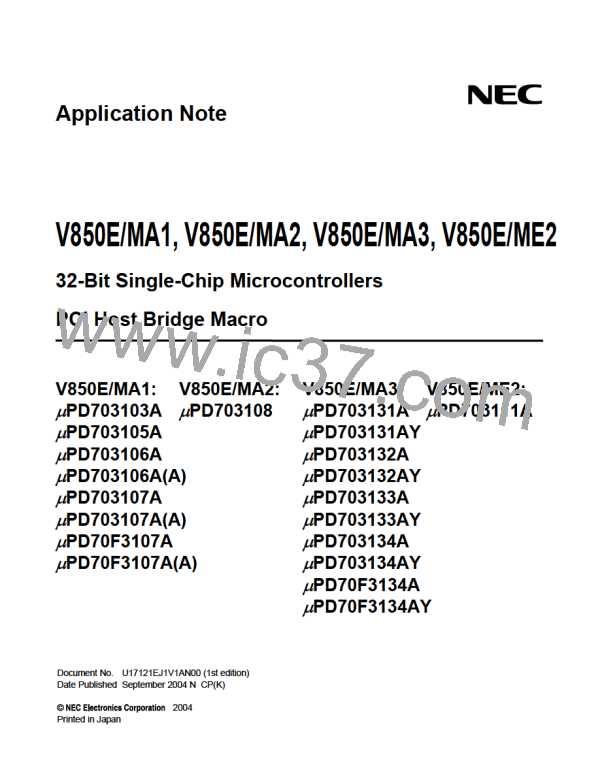

NEC [ NEC ]

NEC [ NEC ]