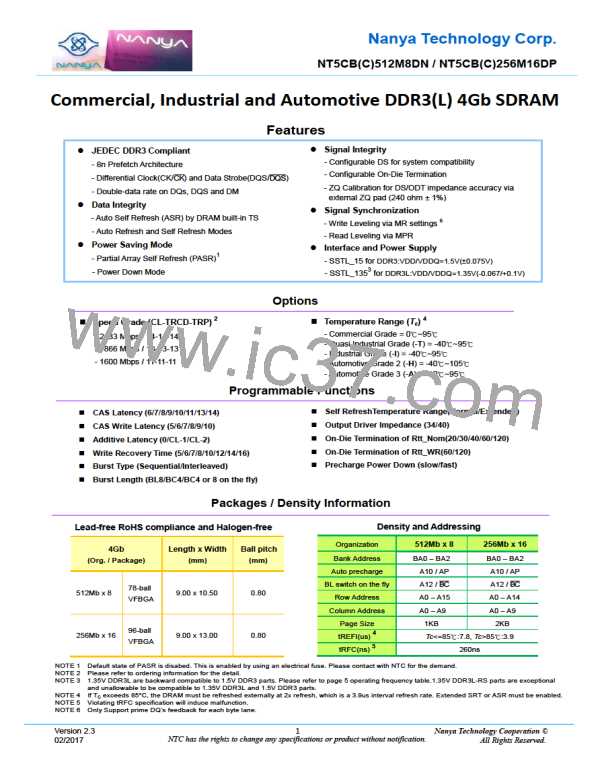

DDR3(L) 4Gb SDRAM

NT5CB(C)512M8DN / NT5CB(C)256M16DP

DDR3 Allowed time before ringback (tDVAC) for CK - and DQS -

DDR3-800 / 1066 / 1333 / 1600

DDR3-1866 / 2133

Slew Rate

[V/ns]

tDVAC [ps]

@ |VIH/Ldiff(AC)| =

350mV

tDVAC [ ps ]

@ |VIH/Ldiff(AC)| =

300mV

tDVAC [ ps ]

@ |VIH/Ldiff(AC)| =

tDVAC [ ps ]

@ |VIH/Ldiff(AC)| =

300mV

tDVAC [ ps ]

@ |VIH/Ldiff(AC)| =

(CK - ) only

(DQS - ) only

Min

Max

Min

175

170

167

119

102

81

Max

Min

214

214

191

146

131

113

88

Max

Min

134

134

112

67

Max

Min

139

139

118

77

Max

> 4.0

4.0

75

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

57

3.0

50

2.0

38

1.8

34

52

63

1.6

29

33

45

1.4

22

54

9

23

1.2

note

note

note

19

56

note

note

note

note

note

note

1.0

note

note

11

< 1.0

note

NOTE 1. Rising input differential signal shall become equal to or greater than VIHdiff(ac) level and Falling input differential signal shall become

equal to or less than VILdiff(ac) level.

Version 2.3

02/2017

99

Nanya Technology Cooperation ©

All Rights Reserved.

NANYA [ Nanya Technology Corporation. ]

NANYA [ Nanya Technology Corporation. ]