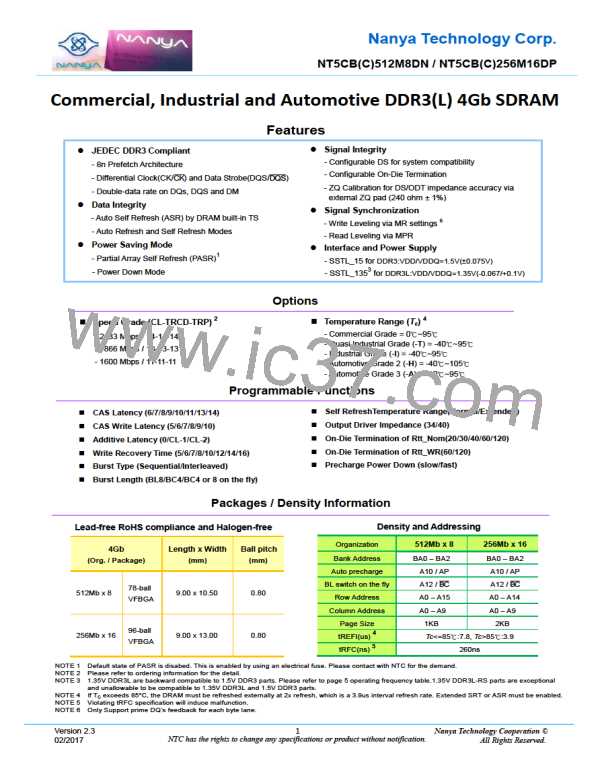

DDR3(L) 4Gb SDRAM

NT5CB(C)512M8DN / NT5CB(C)256M16DP

Single-ended requirements for differential signals

Each individual component of a differential signal (CK, DQS, DQSL, DQSU, , ,L, or U) has also to comply

with certain requirements for single-ended signals.

CK and have to approximately reach VSEHmin / VSELmax (approximately equal to the ac-levels (VIH (ac) / VIL (ac)) for

ADD/CMD signals) in every half-cycle. DQS, DQSL, DQSU, , L have to reach VSEHmin / VSELmax (approxi-

mately the ac-levels (VIH (ac) / VIL (ac)) for DQ signals) in every half-cycle proceeding and following a valid transition.

Note that the applicable ac-levels for ADD/CMD and DQ’s might be different per speed-bin etc. E.g., if VIH150

(ac)/VIL150(ac) is used for ADD/CMD signals, then these ac-levels apply also for the single ended signals CK and

Version 2.3

02/2017

101

Nanya Technology Cooperation ©

All Rights Reserved.

NANYA [ Nanya Technology Corporation. ]

NANYA [ Nanya Technology Corporation. ]