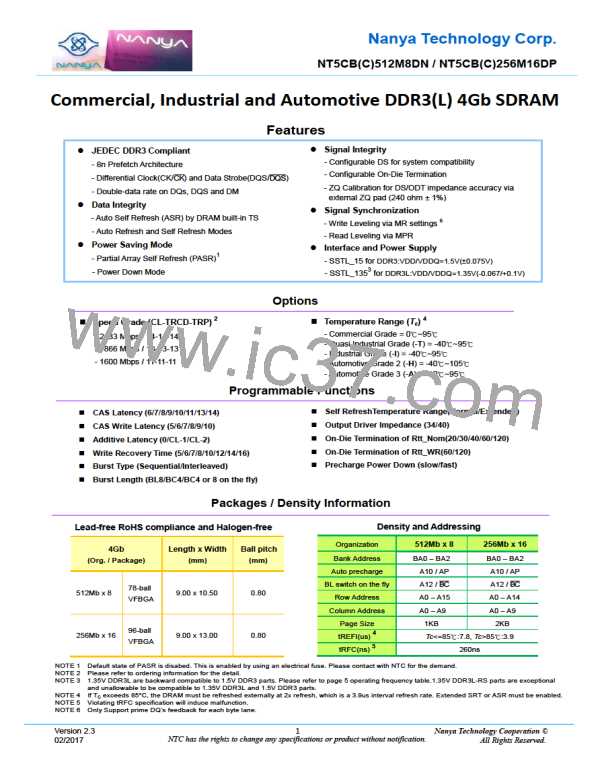

DDR3(L) 4Gb SDRAM

NT5CB(C)512M8DN / NT5CB(C)256M16DP

DDR3 Differential AC and DC Input Levels for clock (CK - ) and strobe (DQS - )

DDR3-800, 1066, 1333, & 1600

Symbol

Parameter

Unit

Notes

Min

+ 0.200

Max

Note 3

1

1

2

2

VIHdiff

VILdiff

Differential input high

Differential input logic low

Differential input high ac

Differential input low ac

V

V

V

V

Note 3

- 0.200

VIHdiff(ac)

VILdiff(ac)

2 x (VIH(ac) - Vref)

Note 3

Note 3

2 x (VIL(ac) - Vref)

NOTE 1. Used to define a differential signal slew-rate.

NOTE 2. For CK - use VIH/VIL(ac) of ADD/CMD and VREFCA; for DQS - , DQSL, L, DQSU ,U use VIH/VIL(ac) of

DQs and VREFDQ; if a reduced ac-high or ac-low level is used for a signal group,then the reduced level applies also here.

NOTE 3. These values are not defined; however, the single-ended signals CK, , DQS, , DQSL, L, DQSU,

U need to be within the respective limits (VIH(dc) max, VIL(dc)min) for single-ended signals as well as the limitations for

overshoot and undershoot. Refer to “Overshoot and Undershoot Specifications”

DDR3L Differential AC and DC Input Levels for clock (CK - ) and strobe (DQS - )

DDR3L-800, 1066, 1333, 1600 & 1866

Symbol

Parameter

Unit

Notes

Min

+ 0.180

Max

Note 3

1

1

2

2

VIHdiff

VILdiff

Differential input high

Differential input logic low

Differential input high ac

Differential input low ac

V

V

V

V

Note 3

- 0.180

VIHdiff(ac)

VILdiff(ac)

2 x (VIH(ac) - Vref)

Note 3

Note 3

2 x (VIL(ac) - Vref)

NOTE 1 Used to define a differential signal slew-rate.

NOTE 2 For CK - use VIH/VIL(AC) of ADD/CMD and VREFCA; for DQS - , DQSL, L, DQSU , U use VIH/VIL(AC) of

DQs and VREFDQ; if a reduced AC-high or AC-low level is used for a signal group, then the reduced level applies also here.

NOTE 3 These values are not defined, however the single-ended signals CK, , DQS, , DQSL, L, DQSU, U need to be

within the respective limits (VIH(DC) max, VIL(DC)min) for single-ended signals as well as the limitations for overshoot and

undershoot. Refer to “Overshoot and Undershoot Specifications”.

Version 2.3

02/2017

97

Nanya Technology Cooperation ©

All Rights Reserved.

NANYA [ Nanya Technology Corporation. ]

NANYA [ Nanya Technology Corporation. ]