MT93L16

Preliminary Information

Address:

38h Read

Send ERROR Peak Detect Register 1 (SEPD1)

7

6

5

4

3

2

1

0

Power Up

Reset 00h

SEPD

SEPD

SEPD

3

SEPD

SEPD

SEPD

0

SEPD

5

SEPD

1

4

6

2

7

MSB

LSB

SEPD

SEPD

SEPD

SEPD

SEPD

SEPD

SEPD

SEPD

0

1

2

3

4

5

6

7

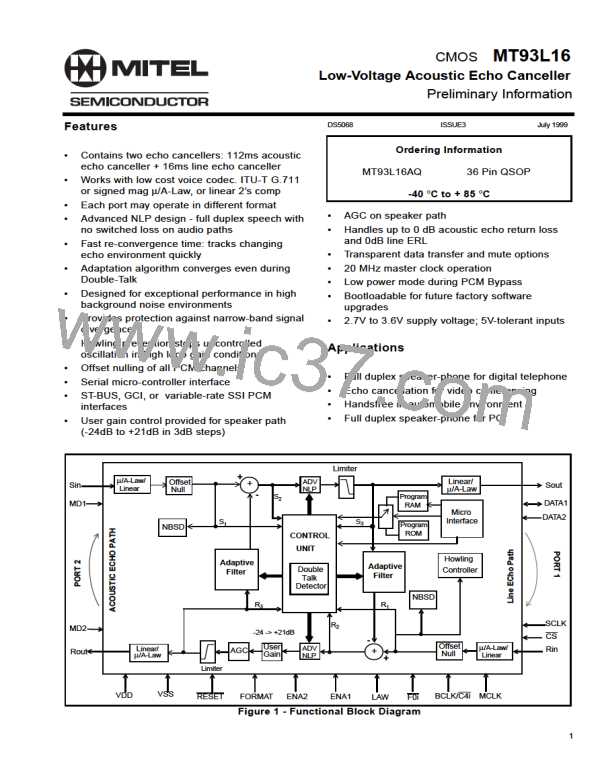

These peak detector registers allow the user to monitor the error signal peak level in the send path at reference point S2

(see Figure #1). The information is in 16-bit 2’s complement linear coded format presented in two 8 bit registers. The high

byte is in Register 2 and the low byte is in Register 1.

Address:

39h Read

Send ERROR Peak Detect Register 2 (SEPD2)

Power Up

Reset 00h

7

6

5

4

3

2

1

0

SEPD

SEPD

8

SEPD

SEPD

SEPD

SEPD

SEPD

10

SEPD

9

12

15

14

13

11

MSB

LSB

SEPD8

SEPD9

SEPD10

SEPD11

SEPD12

SEPD13

SEPD14

SEPD15

See Above description

Address:

1Ah Read

Send (Sout) Peak Detect Register 1 (SOPD1)

7

6

5

4

3

2

1

0

SOPD

Power Up

Reset 00h

SOPD

SOPD

5

SOPD

SOPD

SOPD

SOPD

6

SOPD

2

7

4

3

0

1

MSB

LSB

SOPD

SOPD

SOPD

SOPD

SOPD

SOPD

SOPD

SOPD

0

1

2

3

4

5

6

7

These peak detector registers allow the user to monitor the Send out signal (Sout) peak level at reference point S3 (see

Figure #1). The information is in 16-bit 2’s complement linear coded format presented in two 8 bit registers. The high byte

is in Register 2 and the low byte is in Register 1.

Address:

1Bh Read

Send (Sout) Peak Detect Register 2 (SOPD2)

Power Up

Reset 00h

7

6

5

4

3

2

1

0

SOPD

SOPD

8

SOPD

SOPD

SOPD

SOPD

SOPD

10

SOPD

9

12

15

14

13

11

MSB

LSB

SOPD

SOPD

8

9

SOPD

SOPD

SOPD

SOPD

SOPD

SOPD

10

11

12

13

14

15

See Above description

22

MITEL [ MITEL NETWORKS CORPORATION ]

MITEL [ MITEL NETWORKS CORPORATION ]