MT9160B/61B

Advance Information

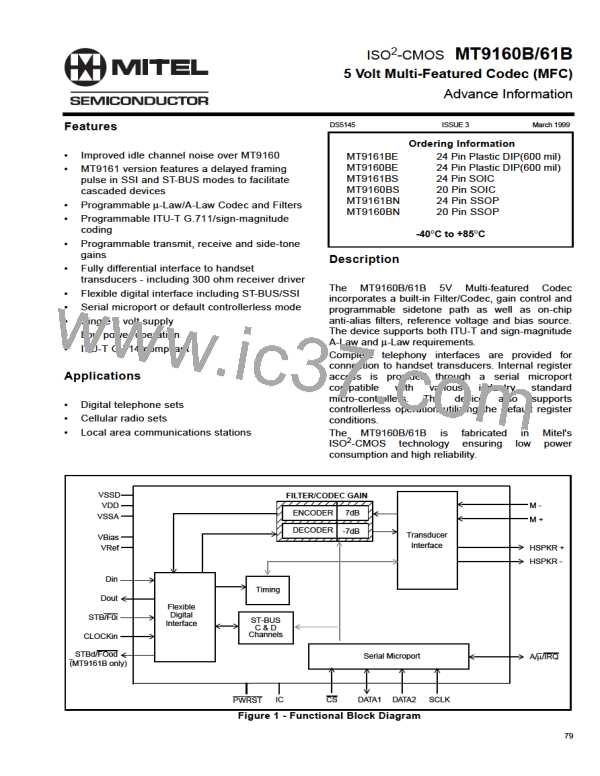

Motorola/National operation. Refer to the relative

timing diagrams of Figures 5 and 6.

Flexible Digital Interface

A serial link is required to transport data between the

MT9160B/61B and an external digital transmission

device. The MT9160B/61B utilizes the ST-BUS

architecture defined by Mitel Semiconductor but also

Receive data is sampled on the rising edge of SCLK

while transmit data is made available concurrent with

the falling edge of SCLK.

➃

➄

COMMAND/ADDRESS

DATA INPUT/OUTPUT

COMMAND/ADDRESS:

➀

➀

DATA 1

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

RECEIVE

D

D

D

D

D

D

D

DATA 1

TRANSMIT

0

1

2

3

4

5

6

7

0

1

2

3

4

5 6

7

②

SCLK

CS

➃

➂

➂

➀

②

Delays due to internal processor timing which are transparent.

The MT9160:-latches received data on the rising edge of SCLK.

-outputs transmit data on the falling edge of SCLK.

➂

The falling edge of CS indicates that a COMMAND/ADDRESS byte will be transmitted from the microprocessor. The

subsequent byte is always data until terminated via CS returning high.

➃

➄

A new COMMAND/ADDRESS byte may be loaded only by CS cycling high then low again.

D

D

0

7

The COMMAND/ADDRESS byte contains: 1 bit - Read/Write

3 bits - Addressing Data

4 bits - Unused

X

X

X

X

A

A

A

0

R/W

2

1

Figure 4 - Serial Port Relative Timing for Intel Mode 0

➃

COMMAND/ADDRESS:

COMMAND/ADDRESS

DATA INPUT/OUTPUT

➄

➀

➀

DATA 2

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

7

6

5

4

3

2

1

0

7

6

5

4

3

2

1

0

7

6

5

4

3

2

1

0

RECEIVE

D

D

D

D

D

D

D

DATA 1

TRANSMIT

7

6

5

4

3

2

1

0

7

6

5

4

3

2 1

0

②

SCLK

CS

➃

➂

➂

➀

②

Delays due to internal processor timing which are transparent.

The MT9160:-latches received data on the rising edge of SCLK.

-outputs transmit data on the falling edge of SCLK.

➂

The falling edge of CS indicates that a COMMAND/ADDRESS byte will be transmitted from the microprocessor. The

subsequent byte is always data until terminated via CS returning high.

➃

➄

A new COMMAND/ADDRESS byte may be loaded only by CS cycling high then low again.

D

D

The COMMAND/ADDRESS byte contains: 1 bit - Read/Write

3 bits - Addressing Data

4 bits - Unused

7

0

A

R/W

X

X

X

A

A

X

2

1

0

Figure 5 - Serial Port Relative Timing for Motorola Mode 00/National Microwire

84

MITEL [ MITEL NETWORKS CORPORATION ]

MITEL [ MITEL NETWORKS CORPORATION ]