MT9160B/61B

Advance Information

MT9160BE

MT9161BE/BS/BN

MT9160BS/BN

VBias

VRef

NC

PWRST

IC

A/µ/IRQ

VSSD

CS

VBias

VRef

NC

PWRST

IC

A/µ/IRQ

VSSD

CS

24

23

22

21

20

19

18

17

16

15

14

13

24

23

22

21

20

19

18

17

16

15

14

13

1

1

2

3

4

5

6

7

8

M +

M -

VSSA

NC

HSPKR +

HSPKR -

VDD

CLOCKin

NC

STB/F0i

Din

M +

M -

VSSA

NC

HSPKR +

HSPKR -

VDD

CLOCKin

STBd/FOod

STB/F0i

Din

2

1

VBias

M +

M -

20

19

3

4

5

6

7

8

9

10

11

12

2

VRef

PWRST

IC

A/µ/IRQ

VSSD

CS

3

4

5

6

7

VSSA

HSPKR +

HSPKR -

VDD

CLOCKin

STB/F0i

Din

18

17

16

15

14

13

12

11

NC

NC

9

8

9

10

SCLK

DATA1

DATA2

SCLK

DATA1

DATA2

SCLK

DATA1

DATA2

10

11

12

Dout

Dout

Dout

20 PIN SOIC/SSOP

24 PIN PDIP

24 PIN PDIP/SOIC/SSOP

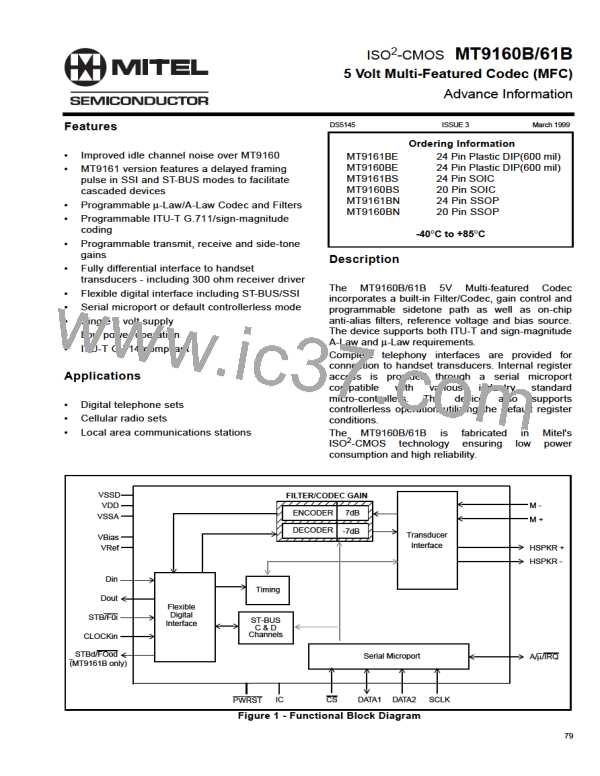

Figure 2 - Pin Connections

Pin Description

Pin # Pin #

20 Pin 24 Pin

Name

Description

Bias Voltage (Output). (V /2) volts is available at this pin for biasing external

1

2

3

1

2

4

V

Bias

DD

amplifiers. Connect 0.1 µF capacitor to V

Connect 1 µF capacitor to Vref.

SSA,

V

Reference Voltage for Codec (Output). Nominally [(V /2)-1.9] volts. Used

DD

Ref

internally. Connect 0.1 µF capacitor to V

Connect 1 µF capacitor to VBias.

SSA,

PWRST Power-up Reset (Input). CMOS compatible input with Schmitt Trigger (active low).

Resets internal state of device.

4

5

5

6

IC

Internal Connection. Tie externally to V

for normal operation.

SSD

A/µ/IRQ A/µ - When internal control bit DEn = 0 this CMOS level compatible input pin

governs the companding law used by the filter/Codec; µ-Law when tied to V

and

SSD

A-Law when tied to V . Logically OR’ed with A/µ register bit.

DD

IRQ - When internal control bit DEn = 1 this pin becomes an open-drain interrupt

output signalling valid access to the D-Channel registers in ST-BUS mode.

6

7

7

8

V

Digital Ground. Nominally 0 volts.

SSD

CS

Chip Select (Input). This input signal is used to select the device for microport

data transfers. Active low. CMOS level compatible.

8

9

10

11

SCLK

Serial Port Synchronous Clock (Input). Data clock for microport. CMOS level

compatible.

DATA 1 Bidirectional Serial Data. Port for microprocessor serial data transfer. In Motorola/

National mode of operation, this pin becomes the data transmit pin only and data

receive is performed on the DATA 2 pin. Input CMOS level compatible.

10

11

12

13

DATA 2 Serial Data Receive. In Motorola/National mode of operation, this pin is used for

data receive. In Intel mode, serial data transmit and receive are performed on the

DATA 1 pin and DATA 2 is disconnected. Input CMOS level compatible.

D

Data Output. A high impedance three-state digital output for 8 bit wide channel

data being sent to the Layer 1 transceiver. Data is shifted out via this pin concurrent

with the rising edge of the bit clock during the timeslot defined by STB, or according

to standard ST-BUS timing.

out

12

14

D

Data Input. A digital input for 8 bit wide channel data received from the Layer 1

transceiver. Data is sampled on the falling edge of the bit clock during the timeslot

defined by STB, or according to standard ST-BUS timing. Input level is CMOS

compatible.

in

80

MITEL [ MITEL NETWORKS CORPORATION ]

MITEL [ MITEL NETWORKS CORPORATION ]