Preliminary Information

MT9075A

data link maintenance channel to be modified and

updates the CRC-4 remainder bits to reflect the

modification. All channel, framing and signalling data

passes through the device unaltered. This is useful

for intermediate point applications of a PCM 30 link

where the data link data is modified, but the error

information transported by the CRC-4 bits must be

passed to the terminating end. In the receive

transparent mode, the received line data is

channelled to DSTo with framing operations

disabled, consequently, the data passes through the

slip buffer and drives DSTo with an arbitrary

alignment.

Device Overview

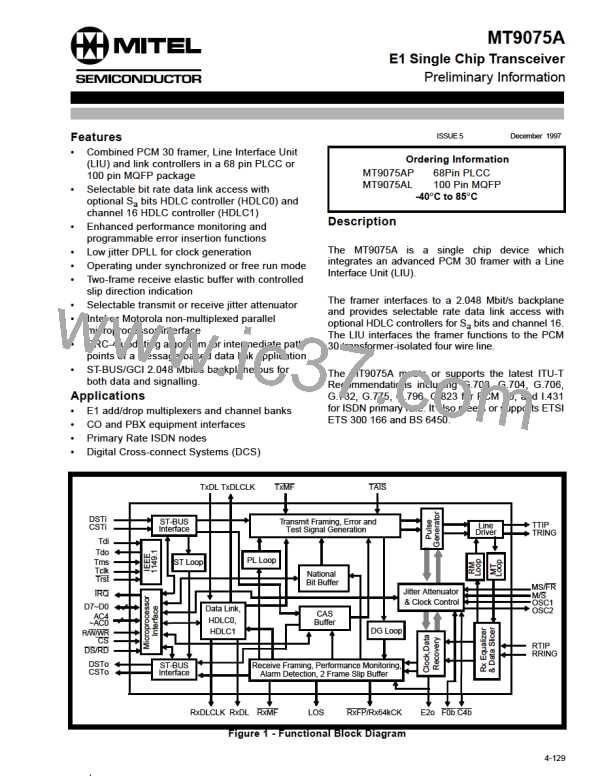

The MT9075A is an advanced PCM 30 framer with

an on-chip Line Interface Unit (LIU) that meets or

supports the latest ITU-T Recommendations for

PCM 30 and ISDN primary rate including G.703,

G.704, G.706, G.775, G.796, G.732, G.823 and

I.431. It also meets or supports the layer 1

requirements of ETSI ETS 300 166 and BS6450.

The Line Interface Unit (LIU) of the MT9075A

interfaces the digital framer functions to the PCM 30

transformer-isolated four wire line. The transmit

portion of the MT9075A LIU consists of a digital

buffer, a digital-to-analog converter and a differential

line driver. The receiver portion of the LIU consists of

an input signal peak detector, an optional two-stage

equalizer, a smoothing filter, data and clock slicers

and a clock extractor. The optional equalizer allows

for error free reception of data with a line attenuation

of up to 20 dB.

The MT9075A has a comprehensive suite of status,

alarm, performance monitoring and reporting

features. These include counters for BPVs, CRC

errors, E-bit errors, errored frame alignment signals,

BERT, and RAI and continuous CRC errors. Also,

included are transmission error insertion for BPVs,

CRC-4 errors, frame and non-frame alignment signal

errors, payload errors and loss of signal errors.

The LIU also contains a Jitter Attenuator (JA), which

can be configured to either the transmit or receive

path. The JA will attenuate jitter from 2.5 Hz and roll-

off at a rate of 20 dB/decade. Its intrinsic jitter is less

than 0.02 UI.

A complete set of loopback functions is provided,

which includes digital, remote, ST-BUS, payload,

metallic, local and remote time slot.

The MT9075A also contains a comprehensive set of

maskable interrupts and an interrupt vector function.

Interrupt sources consist of synchronization status,

alarm status, counter indication and overflow, timer

status, slip indication, maintenance functions and

receive channel associated signalling bit changes. A

special set of maskable interrupts have been

included for sensing changes in the state of the

national use bits and nibbles, in compliance to

emerging ETS requirements.

The digital portion of the MT9075A connects an

incoming stream of time multiplexed PCM channels

(at 2.048 Mbit/s) to the transmit payload of the E1

trunk, while the receive payload is connected to the

ST-BUS or GCI 2.048 Mbit/s backplane bus for both

data and signalling. Control, reporting and

conditioning of the line is implemented via a parallel

microprocessor interface. The MT9075A framing

algorithm allows automatic interworking between

CRC-4 and non-CRC-4 interfaces.

The MT9075A system timing may be slaved to the

line, operated in freerun mode, or controlled by an

external timing source.

The S bits can be accessed by the MT9075A in the

a

following four ways:

•

•

Single byte registers;

Five byte transmit and receive national bit

buffers;

•

•

Data link pins TxDL, RxDL, RxDLCLK and

TxDLCLK;

HDLC Controller with a 128 byte FIFO.

The MT9075A operates in either termination or

transparent modes selectable via software control. In

the termination mode the CRC-4 calculation is

performed as part of the framing algorithm. In the

transmit transparent mode, no framing or signalling

is imposed on the data transmit from DSTi on the

line. In addition, the MT9075A optionally allows the

4-135

MITEL [ MITEL NETWORKS CORPORATION ]

MITEL [ MITEL NETWORKS CORPORATION ]