Advance Information

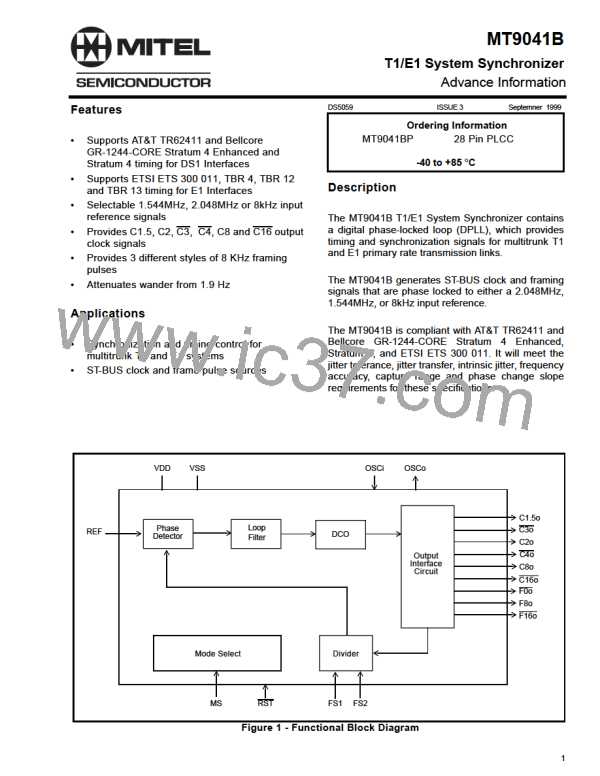

MT9041B

All frame pulse and clock outputs have limited driving

capability, and should be buffered when driving high

capacitance (e.g. 30pF) loads.

Freerun Mode

Freerun Mode is typically used when a master clock

source is required, or immediately following system

power-up before network synchronization is

achieved.

Master Clock

The MT9041B can use either a clock or crystal as

the master timing source. For recommended master

timing circuits, see the Applications - Master Clock

section.

In Freerun Mode, the MT9041B provides timing and

synchronization signals which are based on the

master clock frequency (OSCi) only, and are not

synchronized to the reference signal (REF).

Control and Modes of Operation

The accuracy of the output clock is equal to the

accuracy of the master clock (OSCi). So if a ±32ppm

output clock is required, the master clock must also

be ±32ppm. See Applications - Crystal and Clock

Oscillator sections.

The MT9041B can operate either in Normal or

Freerun modes.

As shown in Table 2, pin MS selects between

NORMAL and FREERUN modes.

MT9041B Measures of Performance

MS

Description of Operation

The following are some synchronizer performance

indicators and their corresponding definitions.

0

1

NORMAL

FREERUN

Intrinsic Jitter

Table 2 - Operating Modes

Intrinsic jitter is the jitter produced by the

synchronizing circuit and is measured at its output. It

is measured by applying a reference signal with no

jitter to the input of the device, and measuring its

output jitter. Intrinsic jitter may also be measured

when the device is in a non-synchronizing mode, i.e.

free running mode, by measuring the output jitter of

the device. Intrinsic jitter is usually measured with

various bandlimiting filters depending on the

applicable standards.

Normal Mode

Normal Mode is typically used when a slave clock

source synchronized to the network is required.

In Normal Mode, the MT9041B provides timing

(C1.5o, C2o, C3o, C4o, C8o and C16o) and frame

synchronization (F0o, F8o, F16o) signals, which are

synchronized to reference input (REF). The input

reference signal may have a nominal frequency of

8kHz, 1.544MHz or 2.048MHz.

Jitter Tolerance

From a reset condition, the MT9041B will take up to

25 seconds for the output signal to be phase locked

to the reference.

Jitter tolerance is a measure of the ability of a PLL to

operate properly (i.e., remain in lock and or regain

lock), in the presence of large jitter magnitudes at

various jitter frequencies applied to its reference.

The applied jitter magnitude and jitter frequency

depends on the applicable standards.

The reference frequencies are selected by the

frequency control pins FS2 and FS1 as shown in

Table 1.

Jitter Transfer

Jitter transfer or jitter attenuation refers to the

magnitude of jitter at the output of a device for a

given amount of jitter at the input of the device. Input

jitter is applied at various amplitudes and

frequencies, and output jitter is measured with

various filters depending on the applicable

standards.

5

MITEL [ MITEL NETWORKS CORPORATION ]

MITEL [ MITEL NETWORKS CORPORATION ]