Advance Information

MT9041B

MT9041B

CLOCK

Out

20MHz ±32ppm

20MHz

MT9074

OSCi

F0o

TTIP

F0i

+ 5V

C4o

C4b

FS1

FS2

MS

TRING

REF

RST

OUT

E1.5o

LOS

IN0

IN1

IN2

IN3

IN4

IN5

IN6

IN7

RTIP

RRING

1kΩ

To Controller

Interrupt

+ 5V

10kΩ

10nF

MT9074

1 TO 8

MUX

TTIP

F0i

C4b

TRING

E1.5o

LOS

RTIP

RRING

To Controller

Interrupt

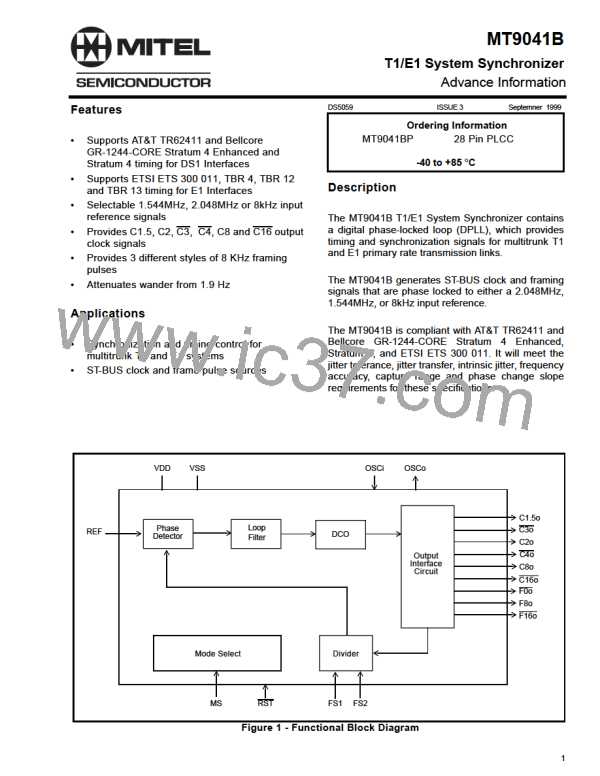

Figure 9 - Multiple E1 Reference Sources with MT9041B

Multiple E1 Reference Sources with MT9041B

In this example 8 E1 link framers (MT9074) are

connected to a common system backplane clock

using the MT9041B. Each of the extracted clocks

E1.5o go to a mux which selects one of the eight

input clocks as the reference to the MT9041B. The

clock choice is made by a controller using the loss of

signal pin LOS from the MT9074s to qualify potential

references. In the event of loss of signal by one of

the framers, an interrupt signals the controller to

choose a different reference clock. Disturbances in

the generated system backplane clocks C4b and F0b

are minimized by the phase slope limitations of the

MT9041B PLL. This ensures system integrity and

minimizes the effect of clock switchover on

downstream trunks.

9

MITEL [ MITEL NETWORKS CORPORATION ]

MITEL [ MITEL NETWORKS CORPORATION ]