ADVANCE

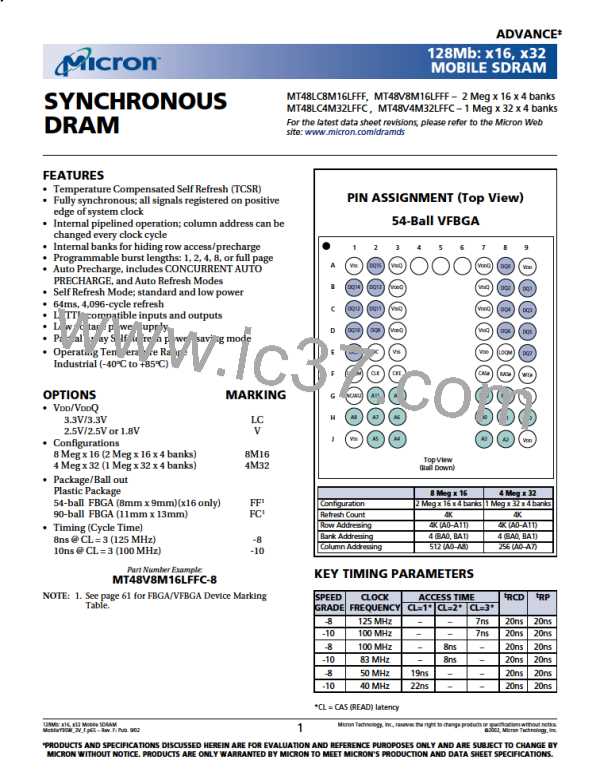

128Mb: x16, x32

MOBILE SDRAM

AC ELECTRICAL CHARACTERISTICS AND OPERATING CONDITIONS

(VDD = +3.3V 0.3V or 2.5 0.2V, VDDQ = +3.3V 0.3V or +2.5V 0.2V or +1.8V 0.15V )

PARAMETER/CONDITION

SYMBOL

VIH

MIN

1.4

–

MAX UNITS NOTES

Input High Voltage: Logic 1; All inputs

Input Low Voltage: Logic 0; All inputs

–

V

V

VIL

0.4

ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS

(Notes: 5, 6, 8, 9, 11; notes appear on page 39)

AC CHARACTERISTICS

PARAMETER

Access time from CLK (pos. edge)

-8

-10

SYMBOL MIN

MAX

7

8

MIN MAX UNITS NOTES

CL = 3 tAC (3)

7

8

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ms

ns

ns

ns

ns

–

27

CL = 2 tAC (2)

CL = 1 tAC (1)

19

22

Address hold time

Address setup time

CLK high-level width

CLK low-level width

Clock cycle time

tAH

1

2.5

3

1

2.5

3

tAS

tCH

tCL

3

3

CL = 3 tCK (3)

8

10

12

25

1

23

23

23

CL = 2 tCK (2)

10

20

1

CL = 1 tCK (1)

CKE hold time

tCKH

CKE setup time

tCKS

2.5

1

2.5

1

2.5

1

2.5

1

CS#, RAS#, CAS#, WE#, DQM hold time

CS#, RAS#, CAS#, WE#, DQM setup time

Data-in hold time

Data-in setup time

Data-out high-impedance time

tCMH

tCMS

tDH

tDS

2.5

2.5

CL = 3 tHZ (3)

7

8

19

7

8

22

10

10

10

CL = 2 tHZ (2)

CL = 1 tHZ (1)

Data-out low-impedance time

Data-out hold time (load)

tLZ

tOH

tOHN

tRAS

tRC

tRCD

tREF

tRFC

tRP

1

1

2.5

1.8

48

80

20

2.5

1.8

50

Data-out hold time (no load)

ACTIVE to PRECHARGE command

ACTIVE to ACTIVE command period

ACTIVE to READ or WRITE delay

Refresh period (4,096 rows)

AUTO REFRESH period

PRECHARGE command period

ACTIVE bank a to ACTIVE bank b command

Transition time

28

120,000

64

120,000

64

100

20

80

20

20

0.5

100

20

20

tRRD

tT

1.2

0.5

1.2

7

24

WRITE recovery time

tWR 1 CLK +

7ns

1 CLK +

5ns

15

80

15

100

ns

ns

25

20

Exit SELF REFRESH to ACTIVE command

tXSR

128Mb: x16, x32 Mobile SDRAM

MobileY95W_3V_F.p65 – Rev. F; Pub. 9/02

Micron Technology, Inc., reserves the right to change products or specifications without notice.

©2002, Micron Technology, Inc.

36

MICRON [ MICRON TECHNOLOGY ]

MICRON [ MICRON TECHNOLOGY ]