Micrel, Inc.

KSZ9021RL/RN

RGMII Signal Definition

The following table describes the RGMII signals. Refer to the RGMII Version 1.3 Specification for more detailed

information.

RGMII

RGMII

Pin Type

(with respect

to PHY)

Pin Type

(with respect

to MAC)

Signal Name Signal Name

Description

(per spec)

(per KSZ9021RL/RN)

TXC

GTX_CLK

Input

Output

Transmit Reference Clock

(125MHz for 1000Mbps, 25MHz for

100Mbps, 2.5MHz for 10Mbps)

TX_CTL

TXD[3:0]

RXC

TX_EN

Input

Output

Output

Input

Transmit Control

TXD[3:0]

RX_CLK

Input

Transmit Data [3:0]

Receive Reference Clock

Output

(125MHz for 1000Mbps, 25MHz for

100Mbps, 2.5MHz for 10Mbps)

RX_CTL

RXD[3:0]

RX_DV

Output

Output

Input

Input

Receive Control

RXD[3:0]

Receive Data [3:0]

Table 3. RGMII Signal Definition

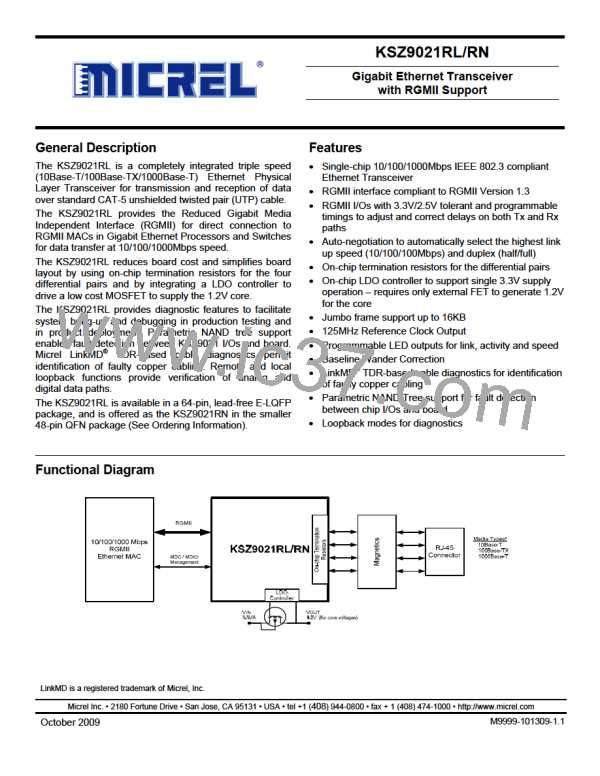

RGMII Signal Diagram

The KSZ9021RL/RN RGMII pin connections to the MAC are shown in the following figure.

RGMII

KSZ9021RL/RN

Ethernet MAC

TXC

GTX_CLK

TX_EN

TX_CTL

TXD[3:0]

TXD[3:0]

RX_CLK

RX_DV

RXC

RX_CTL

RXD[3:0]

RXD[3:0]

Figure 4. KSZ9021RL/RN RGMII Interface

M9999-101309-1.1

October 2009

29

MICREL [ MICREL SEMICONDUCTOR ]

MICREL [ MICREL SEMICONDUCTOR ]