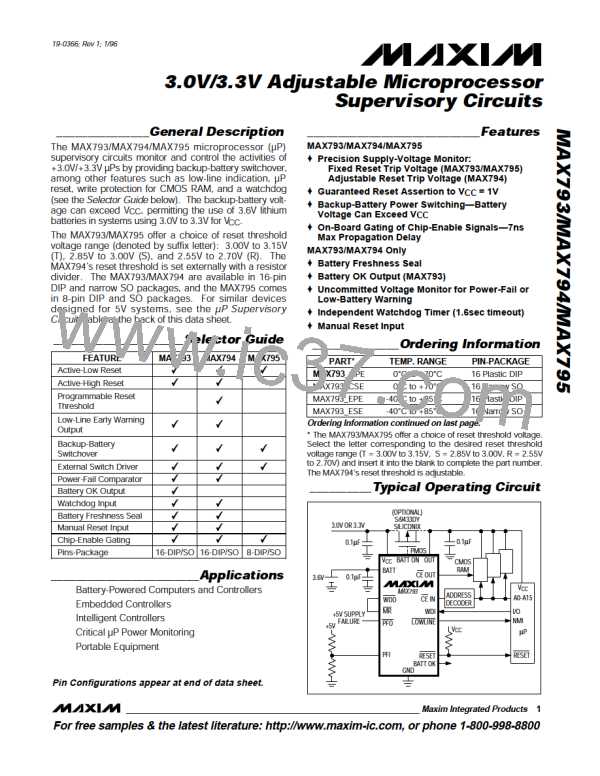

3 .0 V/3 .3 V Ad ju s t a b le Mic ro p ro c e s s o r

S u p e rvis o ry Circ u it s

34/MAX795

V

IN

V

IN

R1

R2

V

V

CC

R1

R2

CC

PFI

MAX793

MAX794

MAX793

MAX794

PFI

R3

R3

C1*

C1*

PFO

PFO

GND

GND

*OPTIONAL

*OPTIONAL

V

TO µP

TO µP

PFO

0V

PFO

0V

V

IN

IN

V

TRIP

V

H

V

L

V

H

0V

0V

V

TRIP

R1 + R2

V

= V

(

)

R1 + R2

R2

TRIP

PFT

R2

V

= V

PFT

(

)

TRIP

WHERE V = 1.237V

PFT

V

1

1

1

D

V

= 10mV

+

+

–

PFH

V = R1 (V + V )

PFT PFH

1

1

1

(

)

H

V = (V + V ) (R1)

H

PFT PFH

R3

R1 R2 R3

+

+

(

)

R1 R2 R3

WHERE V = 1.237V

PFT

1

1

1

V

CC

+

+

–

V = R1 V

PFT

(

)

L

V

= 10mV

PFH

R1 R2 R3

R3

V

D

= DIODE FORWARD VOLTAGE DROP

(a)

(b)

V = V

L

TRIP

Figure 16. Adding Hysteresis to the Power-Fail Comparator: (a) Symmetrical Hysteresis, (b) Hysteresis Only on Rising V

IN

timeout period (because PFI is below the PFI thresh-

old), the IC will test the voltage level on PFO, find that it

is low, and incorrectly decide to enter freshness seal

V

CC

mode. If V

is later removed, the backup battery will

CC

not be connected to OUT and any devices powered by

OUT will lose power.

V

CC

V

CC

Applications that do not use the PFO comparator need

not be affected by this problem. Simply connect PFI to

RESET

N

V

CC

and PFO will be driven high during all reset time-

RESET

out periods. Freshness seal mode can be entered only

when PFO is low.

RESET

GENERATOR

The IC is under revision to correct this problem. The

revised IC will disable PFO during all reset timeout peri-

ods including MR-initiated ones. This revision will not

affect applications that either do not use MR or do not

use PFO, but could affect applications that require the

use of the PFO output during MR-initiated reset timeout

periods. The revised ICs are expected to be available

in late 1996. For technical assistance, please contact

Ma xim Ap p lic a tions a t 1-800-998-8800 or a t

http:// www. maxim-ic.com.

µP

MAX793

MAX794

MAX795

GND

GND

Figure 17. Interfacing to µPs with Bidirectional Reset I/O

______________________________________________________________________________________ 17

MAXIM [ MAXIM INTEGRATED PRODUCTS ]

MAXIM [ MAXIM INTEGRATED PRODUCTS ]