3 .0 V/3 .3 V Ad ju s t a b le Mic ro p ro c e s s o r

S u p e rvis o ry Circ u it s

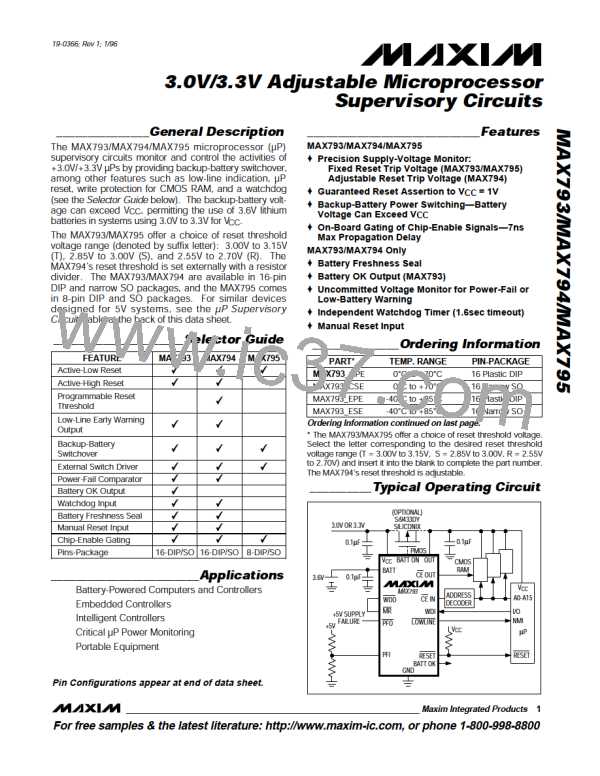

PMOS FET

BODY DIODE

TO CMOS RAM

3.0V OR 3.3V

S

D

G

V

CC

BATT ON OUT

V

CC

BATT ON OUT

MAX793

MAX794

MAX795

MAX793

MAX794

MAX795

GND

GND

(a)

(b)

Figure 14. Driving an External Transistor with BATT ON

3.0V OR 3.3V

+5V

3.0V OR

3.3V

V

MAX793

MAX794

OUT

TO STATIC

RAM

CC

V

MAX793

MAX794

OUT

TO STATIC

RAM

CC

CC

34/MAX795

V

V

CC

1N4148

1N4148

0.47F

BATT

RESET

TO µP

BATT

RESET

TO µP

0.47F

GND

GND

(a)

Figure 15. Using a SuperCap™ as a Backup Source

(b)

The IC decides whether or not to enter freshness seal

mode during all reset timeout periods. During a power-

____________________________Erra t u m

Initial versions of the MAX793 and MAX794 have a

logic design error that can cause the loss of output volt-

up reset timeout period (which occurs when V

is

CC

raised above the MAX793’s reset threshold or the volt-

age on the MAX794’s RESET IN pin is raised above the

RESET IN threshold), the IC momentarily disconnects

the PFO pin from the comparator output and lightly

age (OUT) when V

is absent even though a backup

CC

battery is connected to the BATT input. Applications

that do not use the MR input (including all MAX795

a p p lic a tions ) a re una ffe c te d b y this p he nome non.

Also, applications that do not use PFO are unaffected if

pulls PFO up to V . The voltage level on the PFO pin

CC

is then tested and, if it is low, freshness seal mode is

chosen. (PFO is reconnected to the comparator output

before the end of the reset timeout period.)

PFI is tied to V

.

CC

The loss of output voltage is caused by the IC incor-

re c tly e nte ring the b a tte ry “fre s hne s s s e a l” mod e .

Normally, freshness seal mode is activated by ground-

ing PFO during a power-up reset timeout period. Then,

However, when a reset is initiated by MR, the PFO pin

incorrectly remains connected to the comparator output

during the entire timeout period and is not pulled up. If

the comparator is driving PFO low during an MR reset

the removal of V

powers the IC down without con-

CC

necting the backup battery to OUT.

16 ______________________________________________________________________________________

MAXIM [ MAXIM INTEGRATED PRODUCTS ]

MAXIM [ MAXIM INTEGRATED PRODUCTS ]