ML1451xx

LANSDALE Semiconductor, Inc.

TIMING REQUIREMENTS (Input t = t = 10 ns unless otherwise indicated)

r

f

V

DD

V

Guaranteed Limit

25 C

Guaranteed Limit

– 40 to 85 C

Symbol

Parameter

Unit

f

Serial Data Clock Frequency, Assuming 25% Duty Cycle

3

5

9

DC to 5.0

DC to 7.1

DC to 10

DC to 3.5

DC to 7.1

DC to 10

MHz

clk

NOTE: Refer to CLK t

(Figure 6)

below

w(H)

t

Minimum Setup Time, Data to CLK

(Figure 7)

3

5

9

30

20

18

30

20

18

ns

ns

ns

ns

ns

µs

su

t

Minimum Hold Time, CLK to Data

(Figure 7)

3

5

9

40

20

15

40

20

15

h

t

su

Minimum Setup Time, CLK to ENB

(Figure 7)

3

5

9

70

32

25

70

32

25

t

Minimum Recovery Time, ENB to CLK

(Figure 7)

3

5

9

5

10

20

5

10

20

rec

t

Minimum Pulse Width, CLK and ENB

(Figure 6)

3

5

9

50

35

25

70

35

25

w(H)

t , t

r f

Maximum Input Rise and Fall Times – Any Input

(Figure 8)

3

5

9

5

4

2

5

4

2

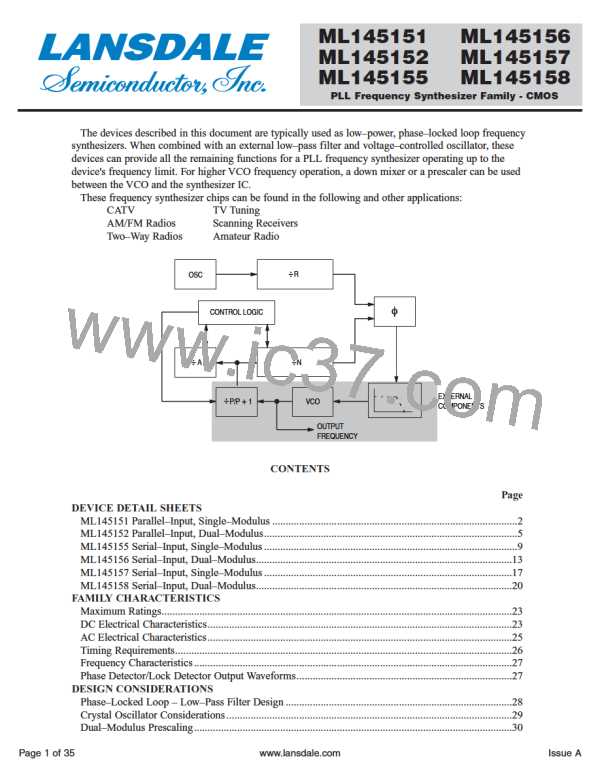

SWITCHING WAVEFORMS

– V

DD

t

DATA

w(H)

50%

– V

DD

V

SS

CLK,

ENB

t

su

50%

t

h

V

*

SS

1

– V

DD

4 f

clk

LAST

CLK

FIRST

CLK

CLK

ENB

50%

V

SS

*Assumes 25% Duty Cycle.

t

t

su

rec

– V

DD

Figure 6.

50%

V

SS

PREVIOUS

DATA

LATCHED

t

t

f

r

ANY

OUTPUT

– V

DD

90%

10%

Figure 7.

V

SS

Figure 8.

Page 26 of 35

www.lansdale.com

Issue A

LANSDALE [ LANSDALE SEMICONDUCTOR INC. ]

LANSDALE [ LANSDALE SEMICONDUCTOR INC. ]