IDT70825S/L

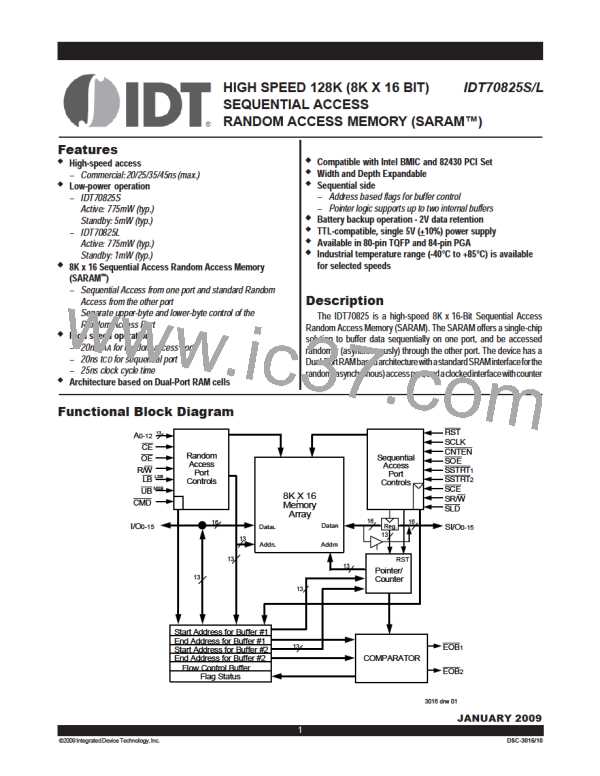

High-Speed 8K x 16 Sequential Access Random Access Memory

Industrial and Commercial Temperature Ranges

Random Access Port - Reset Timing

tRSPW

RST

tRSRC

R/W, SR/W CMD

or (UB + LB)(4)

tWERS

tRSFV

EOB(1 or 2)

Flag Valid

3016 drw 25

Random Access Port Restart Timing of Sequential Port(1)

0.5 x tCYC

tFS

SCLK

R/W

(2)

2-5ns

6-7ns

(3)

CLR

Block

3016 drw 26

(Internal Signal)

NOTES:

1. The sequential port is in the STOP mode and is being restarted from the random port by the Bit 4 Counter Release (see Case 5).

2. "0" is written to Bit 4 from the random port at address [A2 - A0] = 100, when CMD = VIL and CE = VIH. The device is in the Buffer Command Mode

(see Case 5).

3. CLR is an internal signal only and is shown for reference only.

4. Sequential port must also prohibit SR/W or SCE from being LOW for tWERS and tRSRC periods, or SCLK must not toggle from LOW-to-HIGH until after tRSRC.

20

IDT [ INTEGRATED DEVICE TECHNOLOGY ]

IDT [ INTEGRATED DEVICE TECHNOLOGY ]