IDT70825S/L

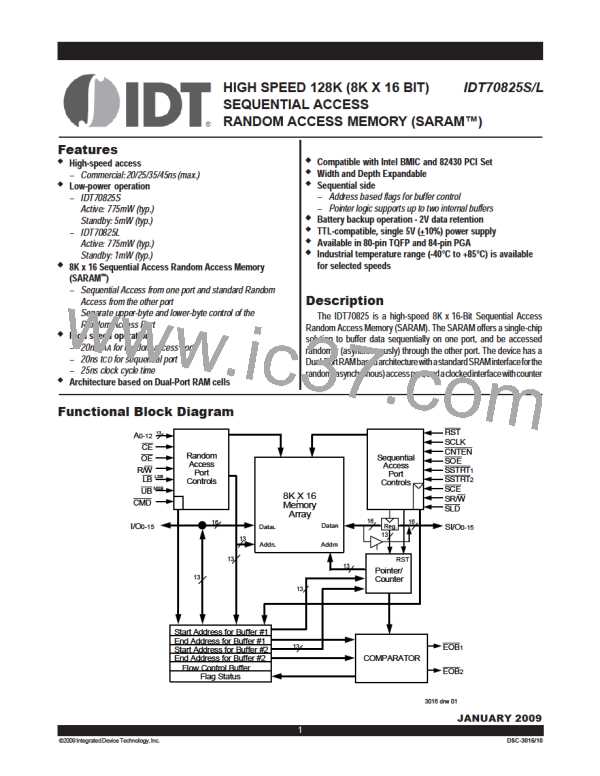

High-Speed 8K x 16 Sequential Access Random Access Memory

Industrial and Commercial Temperature Ranges

Waveform of Write Cycles: Sequential Port

t

CYC

t

CH

tCL

SCLK

CNTEN

SLD

tEH

t

EH

(4)

t

ES

tES

(3)

tEH

t

ES

(1)

t

DS

t

DS

t

DS

tDH

t

DH

t

DH

HIGH IMPEDANCE

SI/OIN

Dx

A0

D0

D1

tWS

t

WS

tWH

t

WH

(4)

SR/W

SCE

tWS

tWS

tWH

tWH

tCKHZ

t

CD

(5)

SOE

t

OHZ

HIGH IMPEDANCE

SI/OOUT

D0

3016 drw 20

tCKLZ

Waveform of Burst Write Cycles: Sequential Port

tCYC

tCH

tCL

SCLK

t

EH

tES

(3)

(2)

CNTEN

SLD

tES

t

EH

(1)

t

DS

t

DS

t

DH

tDH

SI/OIN

Dx

A0

D0

D1

D2

tWS

tWS

t

WH

t

WH

SR/W

(5)

t

WS

t

WS

tWH

t

WH

SCE

SOE

(5)

tCKLZ

tCD

HIGH IMPEDANCE

SI/OOUT

D2

3016 drw 21

NOTES :

1. If SLD = VIL, then address will be clocked in on the SCLK's rising edge.

2. If CNTEN = VIH for the SCLK's rising edge, the internal address counter will not advance.

3. Pointer is not incrementing on cycle immediately following SLD even if CNTEN is LOW.

4. If SR/W = VIL, data would be written to D0 again since CNTEN = VIH.

5. SOE = VIL makes no difference at this point since the SR/W = VIL disables the output until SR/W = VIH is clocked in on the next rising clock edge.

6.42

17

IDT [ INTEGRATED DEVICE TECHNOLOGY ]

IDT [ INTEGRATED DEVICE TECHNOLOGY ]