IDT70825S/L

High-Speed 8K x 16 Sequential Access Random Access Memory

Industrial and Commercial Temperature Ranges

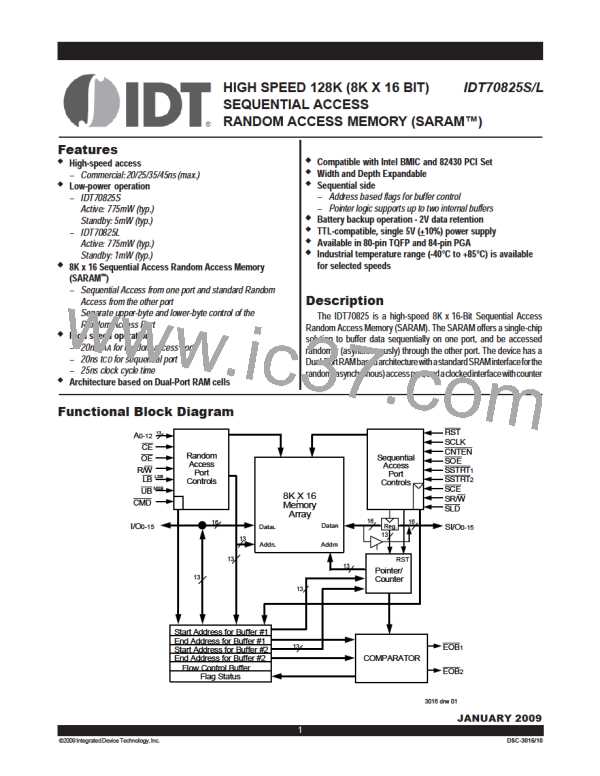

Waveform of Write Cycles: Sequential Port (STRT/EOB Flag Timing)

tCH

tCL

SCLK

tEH

tES

(4)

(2)

CNTEN

tES

tEH

(1)

SSTRT1/2

tDS

tDH

HIGH IMPEDANCE

D0

D1

Dx

D2

SI/OIN

D3

t

WS

tWS

tWH

tWH

(5)

SR/W

SCE

SOE

tWS

t

WS

t

WH

tWH

(3)

(6)

t

CKLZ

tCD

HIGH IMPEDANCE

D3

SI/OOUT

tEB

EOB1/2

3016 drw 22

NOTES: (Also used in the Figure "Read STRT/EOB Flag Timing")

1. If SSTRT1 or SSTRT2 = VIL, then address will be clocked in on the SCLK's rising edge.

2. If CNTEN = VIH for the SCLK's rising edge, the internal address counter will not advance.

3. SOE will control the output and should be HIGH on power-up. If SCE = VIL and is clocked in while SR/W = VIH, the data addressed will be read out within that cycle. If

SCE = VIL and is clocked in while SR/W = VIL, the data addressed will be written to if the last cycle was a read. SOE may be used to control the bus contention and

permit a write on this cycle.

4. Unlike SLD case, CNTEN is not disabled on cycle immediately following SSTRT.

5. If SR/W = VIL, data would be written to D0 again since CNTEN = VIH.

6. SOE = VIL makes no difference at this point since the SR/W = VIL disables the output until SR/W = VIH is clocked in on the next rising clock edge.

18

IDT [ INTEGRATED DEVICE TECHNOLOGY ]

IDT [ INTEGRATED DEVICE TECHNOLOGY ]