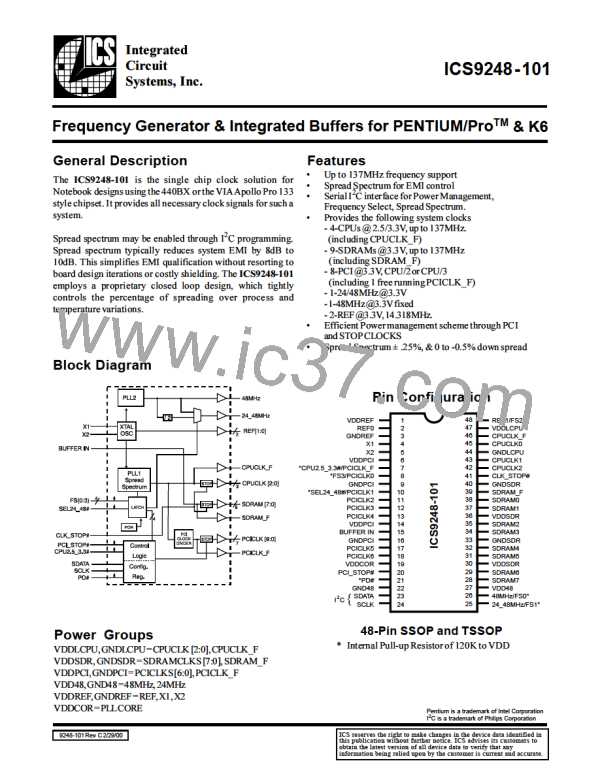

ICS9248-101

Byte 4: Reserved Active/Inactive Register (1 = enable, 0 = disable)

Bit

Pin #

PWD

1

1

1

1

X

1

X

1

Description

(Reserved)

(Reserved)

(SEL24_48)#

(Reserved)

Latched FS1#

(Reserved)

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

-

-

-

-

-

-

-

-

Latched FS3#

(Reserved)

Byte 5: Peripheral Active/Inactive Register (1 = enable, 0 = disable)

Bit

Pin #

34

35

37

38

26

25

48

2

PWD

Description

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

1

1

1

1

1

1

1

SDRAM3 (Act/Inact)

SDRAM2 (Act/Inact)

SDRAM1 (Act/Inact)

SDRAM0 (Act/Inact)

48MHz (Act/Inact)

24MHz (Act/Inact)

REF1 (Act/Inact)

REF0 (Act/Inact)

Notes:

1. Inactive means outputs are held LOW and are disabled from switching.

2. Latched Frequency Selects (FS#) will be inverted logic load of the input frequency select pin conditions.

6

ICSI [ INTEGRATED CIRCUIT SOLUTION INC ]

ICSI [ INTEGRATED CIRCUIT SOLUTION INC ]