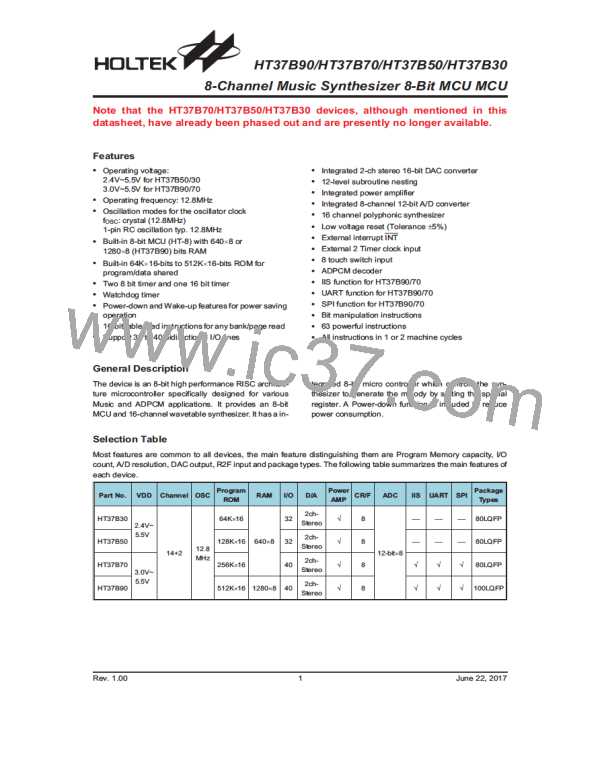

HT37B90/HT37B70/HT37B50/HT37B30

Input/Output Ports and Control Registers -

the end code (80H) until the volume become close. It

provides the left and right volume control independently.

The 10-bit left and right volume are controlled by ENL,

LVC and RVC respectively. The ENV contain both left

and right volume some bit of high byte.

PA, PB, PC, PD, PE, PAC, PBC, PCC, PDC, PEC

Within the area of Special Function Registers, the I/O

registers and their associated control registers play a

prominent role. All I/O ports have a designated register

correspondingly labeled as PA, PB, PC, PD and PE.

These labeled I/O registers are mapped to specific ad-

dresses within the Data Memory as shown in the Data

Memory table, which are used to transfer the appropri-

ate output or input data on that port. with each I/O port

there is an associated control register labeled PAC,

PBC, PCC, PDC and PEC, also mapped to specific ad-

dresses with the Data Memory. The control register

specifies which pins of that port are set as inputs and

which are set as outputs. To setup a pin as an input, the

corresponding bit of the control register must be set

high, for an output it must be set low. During program ini-

tialization, it is important to first setup the control regis-

ters to specify which pins are outputs and which are

inputs before reading data from or writing data to the I/O

ports. One flexible feature of these registers is the ability

to directly program single bits using the ²SET [m].i² and

²CLR [m].i² instructions. The ability to change I/O pins

from output to input and vice versa by manipulating spe-

cific bits of the I/O control registers during normal pro-

gram operation is a useful feature of these devices.

ADPCM Function Registers -

ADR, XSPL, XSPH, ADPC, ADPS

HT37B90/70/50/30 contains ADPCM Decoder Func-

tion. The must set initial value of register known as

XSPL and XSPH before implementing ADPCM Decoder

procedure. There are two 4-bit ADPCM encode data of

ADR. The data of ADR implement via ADPCM Decoder,

and output 8-bit PCM data which is synthesized by MIDI

synthesizer.

The ADPC is the control register for the ADPCM De-

coder. The ADPS is the status register for the ADPCM

Decoder.

CR/F Converter Registers - ASCR, TMRAH, TMRAL,

RCOCCR, TMRBH, TMRBL, RCOCR

There are 8 analog switch lines in the microcontroller for

K0~K7 for HT37B90/70/50/30 Analog Switch control

registers known as ASCR. The RC oscillation converter

contains two 16-bit programmable count-up counters

and the Timer A clock source may come from the sys-

tem clock (fSYS=fOSC/2) or system clock/4 (fOSC/8). There

are two data registers, a high byte data register known

as TMRAH, and a low byte data register known as

TMRAL. The timer B clock source may come from the

external RC oscillator. There are two data registers, a

high byte data register known as TMRBH, and a low

byte data register known as TMRBL. There are two con-

trol and status registers known as RCOCCR and

RCOCR.

D/A Converter Registers - DAH, DAL, DACC

HT37B90/70/50/30 provide two 16-bit D/A converters,

which can select stereo or mono output. The correct op-

eration of the D/A requires the use of two data registers,

and a control register. It contain a 16-bit D/A converter,

there are two data registers, a high byte data register

known as DAH, and a low byte data register known as

DAL. These are the register locations where the digital

value is placed before the completion of a digital to ana-

log conversion cycle. The configuration of the D/A con-

verter is setup via the control register DACC.

A/D Converter Registers -

ADRL, ADRH, ADCR, ACSR

HT37B90/70/50/30 contains a 8-channel 12-bit A/D

converter. The correct operation of the A/D requires the

use of two data registers, a control register and a clock

source register. It contain a 12-bit A/D converter, there

are two data registers, a high byte data register known

as ADRH, and a low byte data register known as ADRL.

These are the register locations where the digital value

is placed after the completion of an analog to digital con-

version cycle. The channel selection and configuration

of the A/D converter is setup via the control register

ADCR while the A/D clock frequency is defined by the

clock source register, ACSR.

Wavetable Function Registers - CHAN, FreqNH,

FreqNL, RepH, RepL, ENV, LVC, RVC

HT37B90/70/50/30 contains Wavetable synthesizer

Function. The HT37B90/70/50/30 has a built-in 16 out-

put channels. CHAN is channel number selection.

FreqNH and FreqNL are used to define the output

speed of the PCM file.

AddrH and AddrL is setup for the start address of the

PCM code before Wavetable function implement. The

repeat number register as known RepH and RepL are

used to define the address which is the repeat point of

the sample. When the repeat number is defined, it will

be output from the start code to the end code once and

always output the range between the repeat address to

Rev. 1.00

20

June 22, 2017

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]

HOLTEK [ HOLTEK SEMICONDUCTOR INC ]