Freescale Semiconductor, Inc.

Serial Communications Interface (SCI)

Functional Description

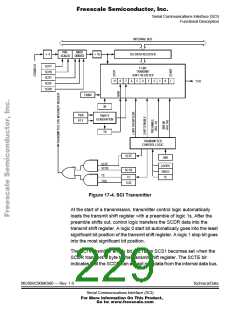

INTERNAL BUS

PRE-

BAUD

÷ 16

÷ 4

SCI DATA REGISTER

SCALER DIVIDER

K

SCP1

SCP0

SCR1

SCR2

SCR0

C

11-BIT

TRANSMIT

SHIFT REGISTER

T

M

P

A

C

S

T

H

8

7

6

5

4

3

2

1

0

L

TxD

B

T

S

TXINV

SM

E

U

M

PEN

PTY

PARITY

GENERATION

T8

TRANSMITTER

CONTROL LOGIC

SCTE

SBK

SCTE

LOOPS

ENSCI

TE

SCTIE

SCTIE

TC

TC

TCIE

TCIE

Figure 17-4. SCI Transmitter

At the start of a transmission, transmitter control logic automatically

loads the transmit shift register with a preamble of logic 1s. After the

preamble shifts out, control logic transfers the SCDR data into the

transmit shift register. A logic 0 start bit automatically goes into the least

significant bit position of the transmit shift register. A logic 1 stop bit goes

into the most significant bit position.

The SCI transmitter empty bit, SCTE, in SCS1 becomes set when the

SCDR transfers a byte to the transmit shift register. The SCTE bit

indicates that the SCDR can accept new data from the internal data bus.

MC68HC908AS60 — Rev. 1.0

Technical Data

Serial Communications Interface (SCI)

For More Information On This Product,

Go to: www.freescale.com

FREESCALE [ Freescale ]

FREESCALE [ Freescale ]