xr

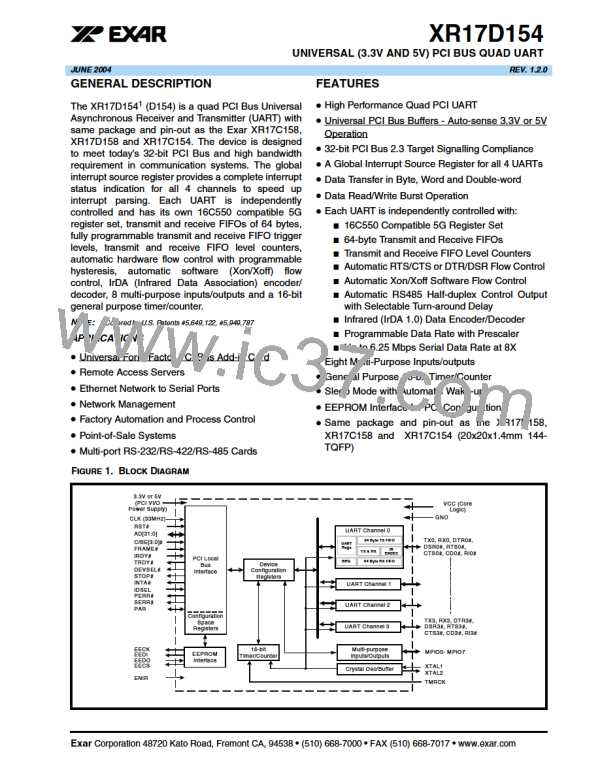

XR17D154

REV. 1.2.0

UNIVERSAL (3.3V AND 5V) PCI BUS QUAD UART

5.8.12 SCRATCH PAD REGISTER (SPR) - Read/Write

This is an 8-bit general purpose register for the user to store temporary data. The content of this register is

preserved during sleep mode but becomes 0xFF (default) after a reset or a power off-on cycle.

5.8.13

FEATURE CONTROL REGISTER (FCTR) - Read/Write

FCTR [3:0] - Auto RTS/DTR Flow Control Hysteresis Select

These bits select the auto RTS/DTR flow control hysteresis and only valid when TX and RX Trigger Table-D is

selected (FCTR bit-6 and 7 are set to logic 1). The RTS/DTR hysteresis is referenced to the RX FIFO trigger

level. After reset, these bits are set to logic 0 selecting the next FIFO trigger level for hardware flow control.

Table 18 shows the 16 selectable hysteresis levels.

FCTR[4]: Infrared RX Input Logic Select

• Logic 0 = Select RX input as active high encoded IrDA data, normal, (default).

• Logic 1 = Select RX input as active low encoded IrDA data, inverted.

FCTR[5]: Auto RS485 Enable

Auto RS485 half duplex control enable/disable.

• Logic 0 = Standard ST16C550 mode. Transmitter generates an interrupt when transmit holding register

(THR) becomes empty. Transmit Shift Register (TSR) may still be shifting data bit out.

• Logic 1 = Enable Auto RS485 half duplex direction control. RTS# output changes its logic level from HIGH to

LOW when finished sending the last stop bit of the last character out of the TSR register. It changes back to

HIGH from LOW when a data byte is loaded into the THR or transmit FIFO. The change to HIGH occurs prior

sending the start-bit. It also changes the transmitter interrupt from transmit holding to transmit shift register

(TSR) empty.

FCTR[7:6]: TX and RX FIFO Trigger Table Select

These 2 bits select the transmit and receive FIFO trigger level table A, B, C or D. When table A, B, or C is

selected the auto RTS flow control trigger level is set to "next FIFO trigger level" for compatibility to ST16C550

and ST16C650 series. RTS#/DTR# triggers on the next level of the RX FIFO trigger level, in another word, one

FIFO level above and one FIFO level below. See Table 15 for complete selection with FCR bit 4-5 and FCTR

bit 6-7, i.e. if Table C is used on the receiver with RX FIFO trigger level set to 56 bytes, RTS/DTR# output will

de-assert at 60 and re-assert at 16.

47

EXAR [ EXAR CORPORATION ]

EXAR [ EXAR CORPORATION ]