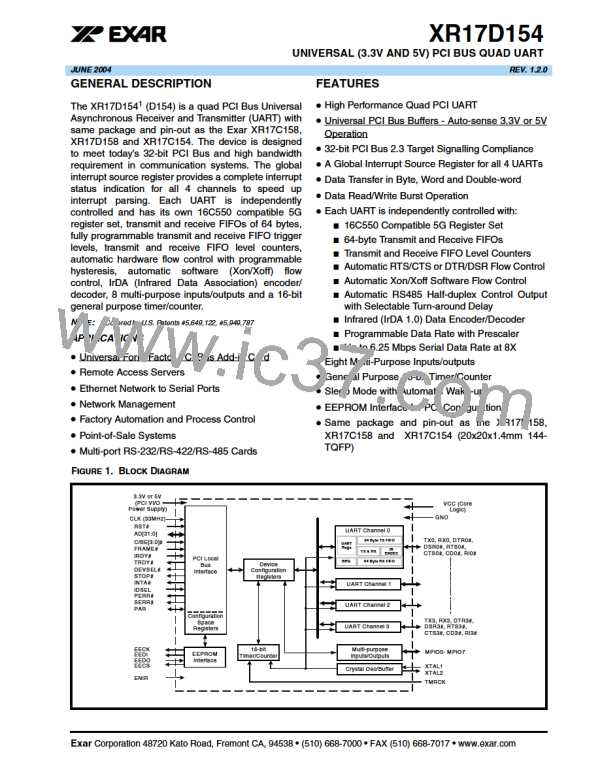

XR17D154

xr

UNIVERSAL (3.3V AND 5V) PCI BUS QUAD UART

REV. 1.2.0

MCR[5]: Xon-Any Enable

• Logic 0 = Disable Xon-Any function (for 16C550 compatibility) (default).

• Logic 1 = Enable Xon-Any function. In this mode any RX character received will enable Xon, resume data

transmission.

MCR[6]: Infrared Encoder/Decoder Enable

The state of this bit depends on the sampled logic level of pin ENIR during power up, following a hardware

reset or a soft-reset. Afterward user can override this bit for desired operation.

• Logic 0 = Disable the infrared mode, operates in the normal serial character mode.

• Logic 1 = Enable infrared IrDA receive and transmit inputs/outputs. While in this mode, the TX/RX output/

input are routed to the infrared encoder/decoder. The data input and output levels will conform to the IrDA

infrared interface requirement. As such, while in this mode the infrared TX output will be a logic 0 during idle

data conditions. FCTR bit-4 may be selected to invert the RX input signal level going to the decoder for

infrared modules that provide rather an inverted output.

MCR[7]: Clock Prescaler Select

• Logic 0 = Divide by one. The input clock from the crystal or external clock is fed directly to the Programmable

Baud Rate Generator without further modification, i.e., divide by one (default).

• Logic 1 = Divide by four. The prescaler divides the input clock from the crystal or external clock by four and

feeds it to the Programmable Baud Rate Generator, hence, data rates become one-fourth.

5.8.9

Line Status Register (LSR) - Read/Only

This register provides the status of data transfers between the UART and the host. If IER bit-2 is set to a logic

1, an LSR interrupt will be generated immediately when any character in the RX FIFO has an error (parity,

framing, overrun, break). Reading LSR will clear LSR bits 4-1.

LSR[0]: Receive Data Ready Indicator

• Logic 0 = No data in receive holding register or FIFO (default).

• Logic 1 = Data has been received and is saved in the receive holding register or FIFO.

LSR[1]: Receiver Overrun Flag

• Logic 0 = No overrun error (default).

• Logic 1 = Overrun error. A data overrun error condition occurred in the receive shift register. This happens

when additional data arrives while the FIFO is full. In this case the previous data in the receive shift register

is overwritten. Note that under this condition the data byte in the receive shift register is not transferred into

the FIFO, therefore the data in the FIFO is not corrupted by the error. This bit is cleared after LSR is read.

LSR[2]: Receive Data Parity Error Tag

• Logic 0 = No parity error (default).

• Logic 1 = Parity error. The receive character in RHR does not have correct parity information and is suspect.

This error is associated with the character available for reading in RHR. This bit is cleared after LSR is read.

LSR[3]: Receive Data Framing Error Tag

• Logic 0 = No framing error (default).

• Logic 1 = Framing error. The receive character did not have a valid stop bit(s). This error is associated with

the character available for reading in RHR. This bit is cleared after LSR is read.

LSR[4]: Receive Break Tag

• Logic 0 = No break condition (default).

• Logic 1 = The receiver received a break signal (RX was a logic 0 for one character frame time). In the FIFO

mode, only one break character is loaded into the FIFO. This bit is cleared after LSR is read.

44

EXAR [ EXAR CORPORATION ]

EXAR [ EXAR CORPORATION ]