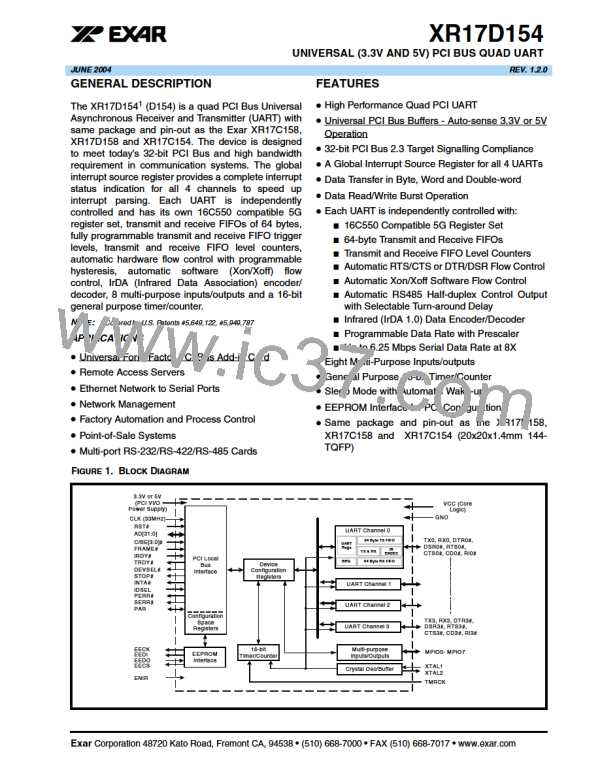

XR17D154

xr

UNIVERSAL (3.3V AND 5V) PCI BUS QUAD UART

REV. 1.2.0

MSR[5]: DSR Input Status

This input may be used for auto DTR/DSR flow control function, see “Section 5.4, Automatic Hardware (RTS/

CTS or DTR/DSR) Flow Control Operation” on page 31 for complete details. If automatic hardware flow control

is not used, this bit is the compliment of the DSR# input. In the loopback mode, this bit is equivalent to the

DTR# bit in the MCR register. The DSR# input may be used as a general purpose input when the modem

interface is not used.

MSR[6]: RI Input Status

This bit is the compliment of the RI# input. In the loopback mode this bit is equivalent to bit-2 in the MCR

register. The RI# input may be used as a general purpose input when the modem interface is not used.

MSR[7]: CD Input Status

This bit is the compliment of the CD# input. In the loopback mode this bit is equivalent to bit-3 in the MCR

register. The CD# input may be used as a general purpose input

5.8.11 Modem Status Register (MSR) - Write-Only

The upper four bits 4-7 of this register sets the delay in number of bits time for the auto RS485 turn around

from transmit to receive.

MSR [7:4]

When Auto RS485 feature is enabled (FCTR bit-5=1) and RTS# output is connected to the enable input of a

RS-485 transceiver. These 4 bits select from 0 to 15 bit-time delay after the end of the last stop-bit of the last

transmitted character. This delay controls when to change the state of RTS# output. This delay is very useful in

long-cable networks. Table 17 shows the selection. The bits are enabled by EFR bit-4.

TABLE 17: AUTO RS485 HALF-DUPLEX DIRECTION CONTROL DELAY FROM TRANSMIT-TO-RECEIVE

MSR[7]

MSR[6]

MSR[5]

MSR[4]

DELAY IN DATA BIT(S) TIME

0

0

0

0

0

9

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

46

EXAR [ EXAR CORPORATION ]

EXAR [ EXAR CORPORATION ]