xr

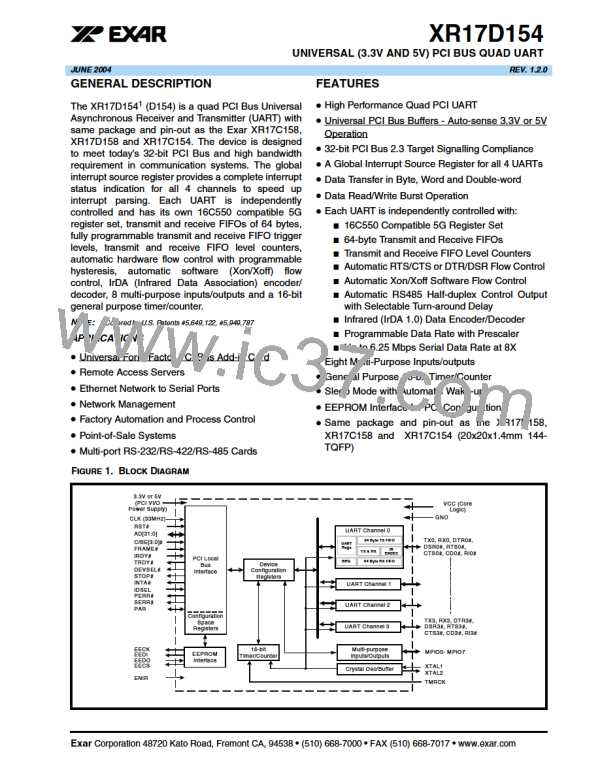

XR17D154

REV. 1.2.0

UNIVERSAL (3.3V AND 5V) PCI BUS QUAD UART

TABLE 20: UART RESET CONDITIONS

RESET STATE

REGISTERS

DLL

Bits 7-0 = 0xXX

Bits 7-0 = 0xXX

Bits 7-0 = 0xXX

Bits 7-0 = 0xXX

Bits 7-0 = 0x00

Bits 7-0 = 0x00

Bits 7-0 = 0x01

Bits 7-0 = 0x00

Bits 7-0 = 0x00

Bits 7-0 = 0x60

Bits 3-0 = logic 0

DLM

RHR

THR

IER

FCR

ISR

LCR

MCR

LSR

MSR

Bits 7-4 = logic levels of the inputs

Bits 7-0 = 0xFF

Bits 7-0 = 0x00

Bits 7-0 = 0x00

Bits 7-0 = 0x00

Bits 7-0 = 0x00

Bits 7-0 = 0x00

Bits 7-0 = 0x00

Bits 7-0 = 0x00

Bits 7-0 = 0x00

Bits 7-0 = 0x00

Bits 7-0 = 0x00

Bits 7-0 = 0x00

RESET STATE

SPR

FCTR

EFR

TXCNT

TXTRG

RXCNT

RXTRG

XCHAR

XON1

XON2

XOFF1

XOFF2

I/O SIGNALS

TX[ch-3:0]

HIGH (if ENIR pin = LOW)

LOW (if ENIR pin = HIGH)

RTS#[ch-3:0]

DTR#[ch-3:0]

EECK

HIGH

HIGH

LOW

LOW

LOW

EECS

EEDI

51

EXAR [ EXAR CORPORATION ]

EXAR [ EXAR CORPORATION ]