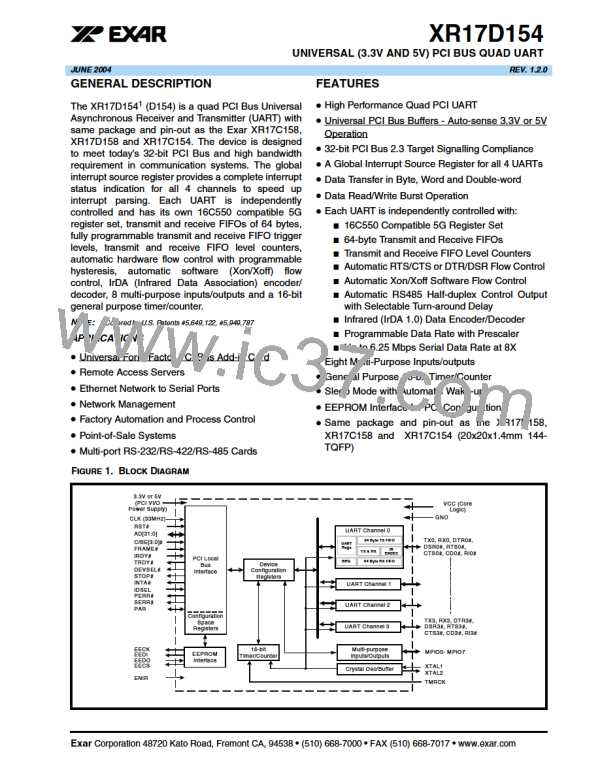

XR17D154

xr

UNIVERSAL (3.3V AND 5V) PCI BUS QUAD UART

REV. 1.2.0

EFR[6]: Auto RTS or DTR Flow Control Enable

RTS#/DTR# output may be used for hardware flow control by setting EFR bit-6 to logic 1. When Auto RTS/

DTR is selected, an interrupt will be generated when the receive FIFO is filled to the programmed trigger level

and RTS#/DTR# will de-assert HIGH at the next upper trigger or selected hysteresis level. RTS#/DTR# will

return LOW when FIFO data falls below the next lower trigger or selected hysteresis level (see FCTR bits 4-7).

The RTS# or DTR# output must be asserted (LOW) before the auto RTS/DTR can take effect. The selection

for RTS# or DTR# is through MCR bit-2. RTS/DTR# pin will function as a general purpose output when

hardware flow control is disabled.

• Logic 0 = Automatic RTS/DTR flow control is disabled (default).

• Logic 1 = Enable Automatic RTS/DTR flow control.

EFR[7]: Auto CTS Flow Control Enable

Automatic CTS or DSR Flow Control.

• Logic 0 = Automatic CTS/DSR flow control is disabled (default).

• Logic 1 = Enable Automatic CTS/DSR flow control. Transmission stops when CTS#/DSR# pin de-asserts

HIGH. Transmission resumes when CTS/DSR# pin returns LOW. The selection for CTS# or DSR# is through

MCR bit-2.

5.8.15 TXCNT[7:0]: Transmit FIFO Level Counter - Read-Only

Transmit FIFO level byte count from 0x00 (zero) to 0x40 (64). This 8-bit register gives an indication of the

number of characters in the transmit FIFO. The FIFO level Byte count register is read only. The user can take

advantage of the FIFO level byte counter for faster data loading to the transmit FIFO, which reduces CPU

bandwidth requirements. Please see the Application Note DAN119 on Exar’s website for a detailed discussion

of FIFO level counters. Due to the dynamic nature of the FIFO counters, this register should be read until the

same value is returned twice.

5.8.16 TXTRG [7:0]: Transmit FIFO Trigger Level - Write-Only

An 8-bit value written to this register sets the TX FIFO trigger level from 0x00 (zero) to 0x40 (64). The TX FIFO

trigger level generates an interrupt whenever the data level in the transmit FIFO falls below this preset trigger

level.

5.8.17 RXCNT[7:0]: Receive FIFO Level Counter - Read-Only

Receive FIFO level byte count from 0x00 (zero) to 0x40 (64). It gives an indication of the number of characters

in the receive FIFO. The FIFO level byte count register is read only. The user can take advantage of the FIFO

level byte counter for faster data unloading from the receiver FIFO, which reduces CPU bandwidth

requirements. Please see the Application Note DAN119 on Exar’s website for a detailed discussion of FIFO

level counters. Due to the dynamic nature of the FIFO counters, this register should be read until the same

value is returned twice.

5.8.18 RXTRG[7:0]: Receive FIFO Trigger Level - Write-Only

An 8-bit value written to this register, sets the RX FIFO trigger level from 0x00 (zero) to 0x40 (64). The RX

FIFO trigger level generates an interrupt whenever the receive FIFO level rises to this preset trigger level.

50

EXAR [ EXAR CORPORATION ]

EXAR [ EXAR CORPORATION ]