áç

ST16C1550/51

2.97V TO 5.5V UART WITH 16-BYTE FIFO

REV. 4.2.0

28-PIN 28-PIN 28-PIN 28-PIN

PLCC PLCC

(1550) (1551) (1550) (1551)

48-PIN

TQFP

NAME

TYPE

DESCRIPTION

PDIP

PDIP

GND

N.C.

15

-

14

-

15

-

14

-

19

Pwr Power supply common ground.

Not connected.

1, 2,

-

10-14,

18,

24-26,

29,

35-38,

42, 44,

48

Pin type: I=Input, O=Output, I/O= Input/output, OD=Output Open Drain.

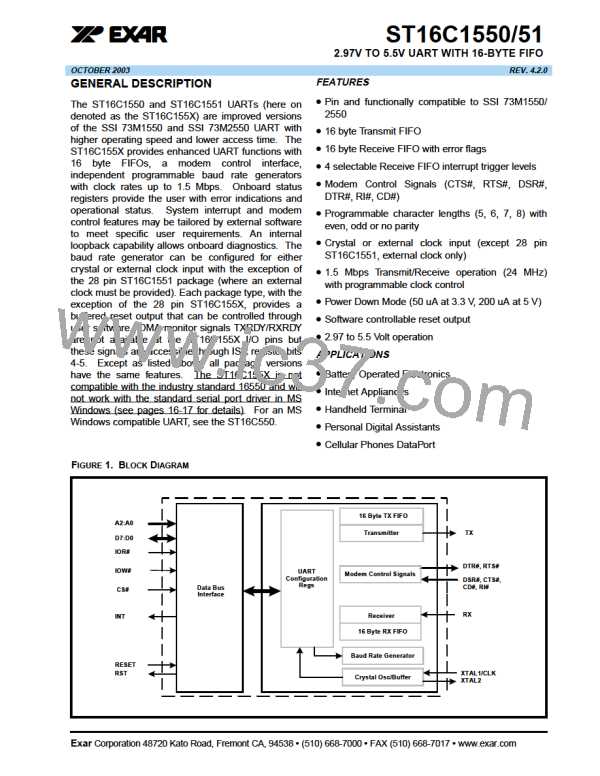

1.0 PRODUCT DESCRIPTION

The ST16C155X provides serial asynchronous receive data synchronization, parallel-to-serial and serial-to-

parallel data conversions for both the transmitter and receiver sections. These functions are necessary for

converting the serial data stream into parallel data that is required in digital data systems. Synchronization for

the serial data stream is accomplished by adding start and stops bits to the transmit data to form a data

character (character orientated protocol). Data integrity is ensured by attaching a parity bit to the data

character. The parity bit is checked by the receiver for any transmission bit errors.

ENHANCED FEATURES

The ST16C155X is an upward solution that provides 16 bytes of transmit and receive FIFO memory, instead of

none in the 16C145X. The 155X is designed to work with high speed modems and shared network

environments, that require fast data processing time. Increased performance is realized in the 155X by the

larger transmit and receive FIFOs. This allows the external processor to handle more networking tasks within a

given time. For example, the ST16C550 with a 16 byte FIFO, unloads 16 bytes of receive data in 93

microseconds (This example uses a character length of 11 bits, including start/stop bits at 115.2Kbps). This

means the external CPU will have to service the receive FIFO less than every 100 microseconds. However

with the 16 byte FIFO in the 155X, the data buffer will not require unloading/loading for 1.53 ms. This increases

the service interval giving the external CPU additional time for other applications and reducing the overall

UART interrupt servicing time. In addition, the 4 selectable levels of FIFO trigger interrupt are provided for

maximum data throughput performance especially when operating in a multi-channel environment. The FIFO

memory greatly reduces the bandwidth requirement of the external controlling CPU, increases performance,

and reduces power consumption.

DATA RATE

The 155X is capable of operation up to 1.5 Mbps with a 24 MHz crystal or external clock input with a 16X

sampling clock (at VCC = 5.0V). With a crystal of 14.7456 MHz and through a software option, the user can

select data rates up to 921.6 Kbps.

The rich feature set of the 155X is available through internal registers. Selectable receive FIFO trigger levels,

selectable baud rates, and modem interface controls are all standard features. Following a power on reset or

an external reset, the 155X is software compatible with the ST16C145X.

7

EXAR [ EXAR CORPORATION ]

EXAR [ EXAR CORPORATION ]