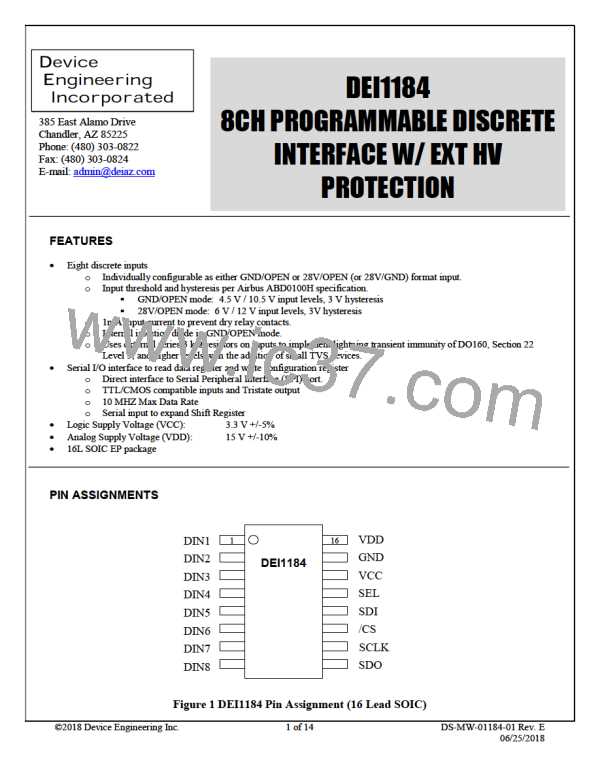

Table 6 AC Electrical Characteristics (4)

PARAMETER CONDITIONS (6,7)

LIMITS

SYMBOL

UNIT

MIN

0.1

MAX

10

fMAX

tW

SCLK frequency. (50% duty cycle) (5)

SCLK pulse width. (5)

MHZ

ns

50

tsu1

th1

tsu2

th2

tsu3

th3

tsu4

th4

tp1

tp2

tp3

Setup time, SCLK low to /CS↓.

Hold time, /CS↓ to SCLK↑.

30

25

500

15

25

25

30

25

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Setup time, DIN valid to /CS↓.

Hold time, /CS↓ to DIN not valid.

Setup time, SDIN valid to SCLK↑.

Hold time, SCLK↑ to SDIN not valid.

Setup time, SEL valid to /CS↓.

Hold time, SEL valid to /CS↑.

Propagation delay, /CS↓ to DOUT valid. (1)

Propagation delay, SCLK↑ to DOUT valid. (1)

Propagation delay, /CS↑ to DOUT HI-Z. (1)

(2) (3)

105

90

80

tp4

Cin

Cout

Delay time between /CS active. (5)

Maximum logic input pin Capacitance. (5)

Maximum DOUT pin capacitance, output in

HI-Z state. (5)

20

ns

pf

pf

10

15

Notes:

1. DOUT loaded with 50 pF to GND.

2. DOUT loaded with 1 kΩ to GND for Hi output, 1 kΩ to VCC for Low output.

3. Timing measured at 25% VCC for “0” to Hi-Z, 75% VCC for “1” to Hi-Z.

4. Sample tested on lot basis.

5. Not tested

6. Ta = -55 to +125 ºC. VCC = 3 V, VDD = 15 V, VIL = 0 V, VIH = VCC unless otherwise noted.

7. Measurements made at 50% VCC.

th4

tsu4

SEL

/CS

tp4

th1

tW

tsu1

SCLK

1/fmax

tsu2

th2

valid

X

X

DIN[1:8]

tsu3

th3

X

valid

X

SDI

tp2

tp1

tp3

D/C0

D/C1

SDO

Figure 11 Switching Waveforms

©2018 Device Engineering Inc.

10 of 14

DS-MW-01184-01 Rev. E

06/25/2018

DEIAZ [ Device Engineering Incorporated ]

DEIAZ [ Device Engineering Incorporated ]