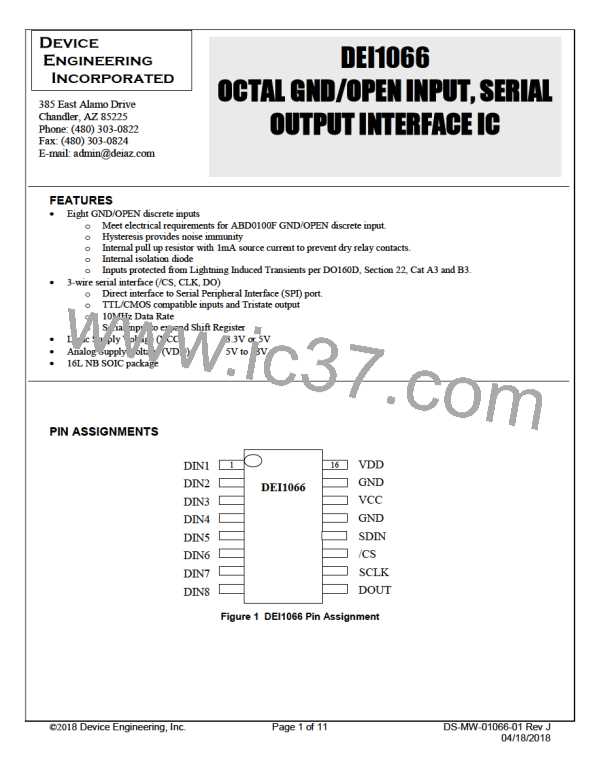

Serial Interface and Shift Register

The DEI1066 digital interface is an 8-Bit Serial or Parallel-Input / Serial-Output Shift Register with 3-State Output. The

control inputs to the shift register are connected as shown in Figure 2 to implement an SPI compatible bus consisting of /CS,

SCLK, DOUT, and SDIN. The Figure 4 waveform depicts a typical 8-Bit read cycle where the 8 DIN signals are read on to

the serial bus. The Figure 5 waveform demonstrates a daisy-chain application where a 16-Bit read cycle includes the serial

data passed through from the SDIN input.

/CS

X

SCLK

X

VALID

X

X

DIN[8:1]

X

X

SDIN

DIN8

DIN7

DIN6

DIN5

DIN4

DIN3

DIN2

DIN1

DOUT

DIN inputs latched in S-Reg

Figure 4 Serial Bus Read Cycle, 8 Bit

/CS

SCLK

X

X

VALID

X

X

DIN[8:1]

SI8

SI7

SI6

SI5

SI4

SI3

SI2

SI1

X

X

SDIN

DIN8

DIN7

DIN6

DIN5

DIN4

DIN3

DIN2

DIN1

SI8

SI7

SI6

SI5

SI4

SI3

SI2

SI1

DOUT

Figure 5 Serial Bus Read Cycle, 16 Bit Daisy Chain

©2018 Device Engineering, Inc.

Page 4 of 11

DS-MW-01066-01 Rev J

04/18/2018

DEIAZ [ Device Engineering Incorporated ]

DEIAZ [ Device Engineering Incorporated ]