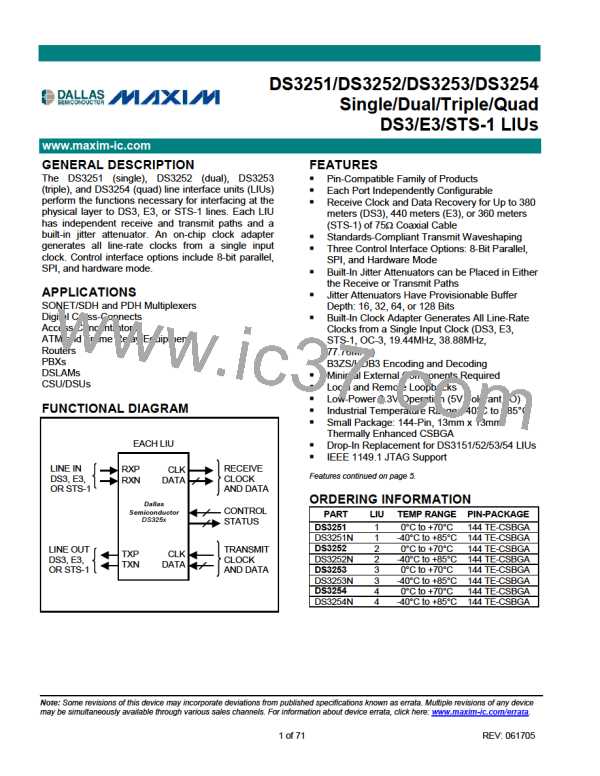

DS3251/DS3252/DS3253/DS3254

FEATURES (CONTINUED)

Receiver

Cꢀ AGC/equalizer block handles from 0 to 15dB of cable loss

Cꢀ Loss-of-lock (LOL) PLL status indication

Cꢀ Interfaces directly to a DSX monitor signal (~20dB flat loss) using built-in preamp

Cꢀ Digital and analog loss-of-signal (LOS) detectors (ANSI T1.231 and ITU G.775)

Cꢀ Optional B3ZS/HDB3 decoder

Cꢀ Line-code violation output pin and counter

Cꢀ Binary or bipolar framer interface

Cꢀ On-board 215 - 1 and 223 - 1 PRBS detector

Cꢀ Clock inversion for glueless interfacing

Cꢀ Tri-state clock and data outputs support protection switching applications

Cꢀ Per-channel power-down control

Transmitter

Cꢀ Binary or bipolar framer interface

Cꢀ Gapped clock capable up to 51.84MHz

Cꢀ Wide 50 M 20% transmit clock duty cycle

Cꢀ Clock inversion for glueless interfacing

Cꢀ Optional B3ZS/HDB3 encoder

Cꢀ On-board 215 - 1 and 223 - 1 PRBS generator

Cꢀ Complete DS3 AIS generator (ANSI T1.107)

Cꢀ Unframed all-ones generator (E3 AIS)

Cꢀ Line build-out (LBO) control

Cꢀ Tri-state line driver outputs support protection switching applications

Cꢀ Per-channel power-down control

Cꢀ Output driver monitor

Jitter Attenuator

Cꢀ On-chip crystal-less jitter attenuator

Cꢀ Meets all applicable ANSI, ITU, ETSI and Telcordia jitter transfer and output jitter requirements

Cꢀ Can be placed in the transmit path, receive path or disabled

Cꢀ Selectable FIFO depth: 16, 32, 64 or 128 bits

Cꢀ Overflow and underflow status indications

Clock Adapter

Cꢀ Operates from a single DS3, E3, STS-1, 19.44 MHz, 38.88 MHz, or 77.76 MHz master clock

Cꢀ Synthesizes clock rates that are not provided externally

Cꢀ Use of common system timing frequencies such as 19.44 MHz eliminates the need for any local oscillators,

reduces cost and board space

Cꢀ Very small jitter gain and intrinsic jitter generation

Cꢀ Optionally provides synthesized clocks on output pins for use by neighboring components, such as framers or

mappers

Parallel CPU Interface

Cꢀ Multiplexed or nonmultiplexed 8-bit interface

Cꢀ Configurable for Intel mode (CS, WR, RD) or Motorola mode (CS, DS, R/W)

SPI CPU Interface

Cꢀ Operation up to 10 Mbit/s

Cꢀ Burst mode for multi-byte read and write accesses

Cꢀ Programmable clock polarity and phase

Cꢀ Half-duplex operation gives option to tie SDI and SDO together externally to reduce wire count

5 of 71

DALLAS [ DALLAS SEMICONDUCTOR ]

DALLAS [ DALLAS SEMICONDUCTOR ]