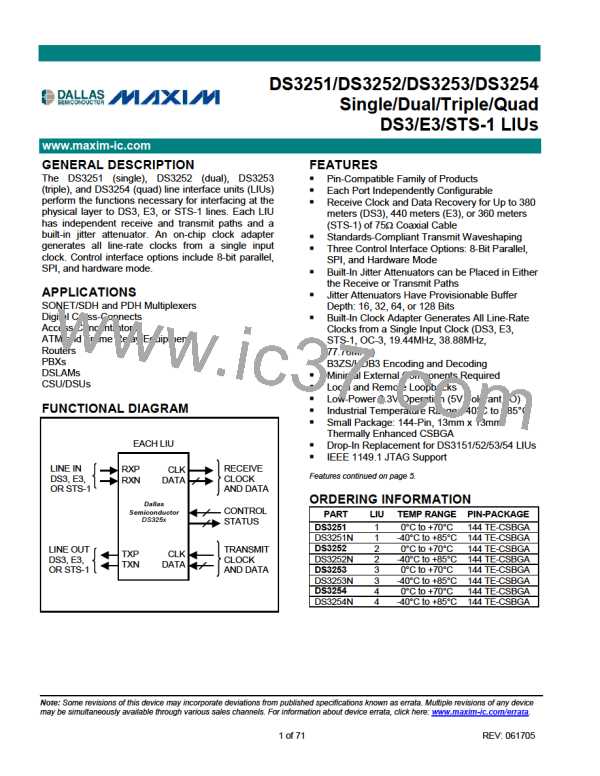

DS3251/DS3252/DS3253/DS3254

TABLE OF CONTENTS

1. STANDARDS COMPLIANCE ......................................................................................................... 6

2. DETAILED DESCRIPTION ............................................................................................................. 7

3. APPLICATION EXAMPLE .............................................................................................................. 7

4. BLOCK DIAGRAMS........................................................................................................................ 8

5. CONTROL INTERFACE MODES.................................................................................................... 9

6. PIN DESCRIPTIONS..................................................................................................................... 10

7. REGISTER DESCRIPTIONS......................................................................................................... 15

8. RECEIVER .................................................................................................................................... 24

8.1

8.2

8.3

8.4

8.5

8.6

8.7

8.8

8.9

INTERFACING TO THE LINE........................................................................................................................... 24

OPTIONAL PREAMP..................................................................................................................................... 24

AUTOMATIC GAIN CONTROL (AGC) AND ADAPTIVE EQUALIZER..................................................................... 24

CLOCK AND DATA RECOVERY (CDR)........................................................................................................... 24

LOSS-OF-SIGNAL (LOS) DETECTOR ............................................................................................................ 24

FRAMER INTERFACE FORMAT AND THE B3ZS/HDB3 DECODER .................................................................... 25

RECEIVE LINE-CODE VIOLATION COUNTER .................................................................................................. 26

RECEIVER POWER-DOWN ........................................................................................................................... 26

RECEIVER JITTER TOLERANCE .................................................................................................................... 26

9. TRANSMITTER............................................................................................................................. 27

9.1

9.2

9.3

9.4

9.5

9.6

9.7

9.8

9.9

TRANSMIT CLOCK ....................................................................................................................................... 27

FRAMER INTERFACE FORMAT AND THE B3ZS/HDB3 ENCODER .................................................................... 27

PATTERN GENERATION ............................................................................................................................... 27

WAVESHAPING, LINE BUILD-OUT, LINE DRIVER............................................................................................ 28

INTERFACING TO THE LINE........................................................................................................................... 28

TRANSMIT DRIVER MONITOR ....................................................................................................................... 28

TRANSMITTER POWER-DOWN...................................................................................................................... 28

TRANSMITTER JITTER GENERATION (INTRINSIC) ........................................................................................... 28

TRANSMITTER JITTER TRANSFER................................................................................................................. 28

JITTER ATTENUATOR............................................................................................................. 32

10.

11.

DIAGNOSTICS.......................................................................................................................... 34

11.1

11.2

PRBS GENERATOR AND DETECTOR............................................................................................................ 34

LOOPBACKS ............................................................................................................................................... 34

CLOCK ADAPTER.................................................................................................................... 35

12.

13.

14.

15.

RESET LOGIC .......................................................................................................................... 35

TRANSFORMERS..................................................................................................................... 36

CPU INTERFACES ................................................................................................................... 37

15.1

15.2

PARALLEL INTERFACE ................................................................................................................................. 37

SPI INTERFACE .......................................................................................................................................... 37

JTAG TEST ACCESS PORT AND BOUNDARY SCAN............................................................ 40

16.

16.1

16.2

16.3

16.4

JTAG DESCRIPTION ................................................................................................................................... 40

JTAG TAP CONTROLLER STATE MACHINE DESCRIPTION............................................................................. 40

JTAG INSTRUCTION REGISTER AND INSTRUCTIONS...................................................................................... 42

JTAG TEST REGISTERS.............................................................................................................................. 43

ELECTRICAL CHARACTERISTICS ......................................................................................... 44

17.

18.

19.

20.

21.

PIN ASSIGNMENTS.................................................................................................................. 56

PACKAGE INFORMATION....................................................................................................... 70

THERMAL INFORMATION ....................................................................................................... 71

REVISION HISTORY................................................................................................................. 71

2 of 71

DALLAS [ DALLAS SEMICONDUCTOR ]

DALLAS [ DALLAS SEMICONDUCTOR ]