CY8C9520A, CY8C9540A

CY8C9560A

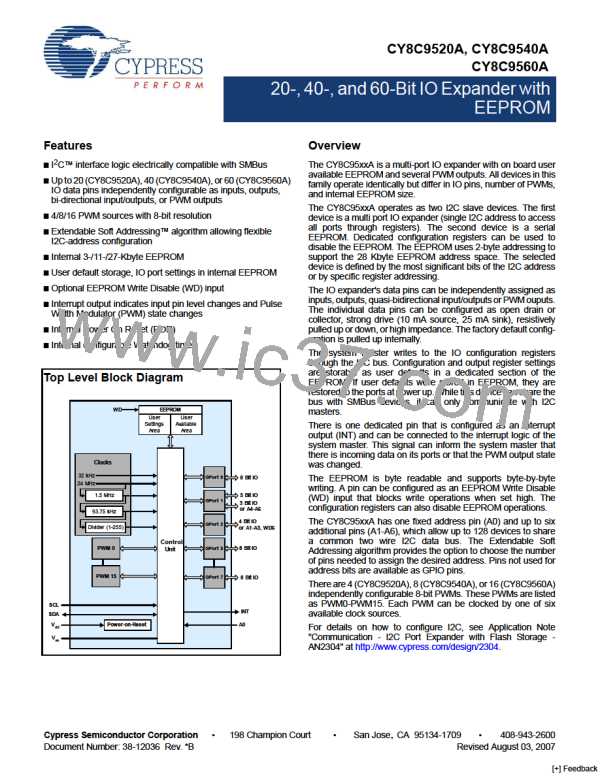

Figure 6. Memory Reading and Writing

Memory Address

Slave Address

R/W

0

R/W

Stop

S

A6 A5 A4 A3 A2 A1 A0

A

High(Addr)

A

Low(Addr)

A

S

A6 A5 A4 A3 A2 A1 A0

1

A

data(Addr)

A

data(Addr+1)

A

...

N

P

Start

ACK from

Slave

ACK from

Slave

ACK from

Slave

ACK from

Slave

ACK from

Master

ACK from

Master

No ACK

from Master

Reading from EEPROM

Up to the End of Address Space

Slave Address

Memory Address

R/W

Stop

S

A6 A5 A4 A3 A2 A1 A0

0

A

High(Addr)

A

Low(Addr)

A

data 1

A

data 2

A

...

A

P

Start

ACK from

Slave

ACK from

Slave

ACK from

Slave

If current address crosses

64-byte block boundary,

then device performs real

writing to EEPROM

Writing to EEPROM

Figure 7. Port Reading and Writing in Multi-Port Device

Slave Address

Register Address = 1

Reading from GPort 2

At this moment, device

performs reading from GPort 1

R/W

R/W

Stop

S

A6 A5 A4 A3 A2 A1 A0

0

A

0

0

0

0

0

0

0

1

A

S

A6 A5 A4 A3 A2 A1 A0

1

A

data from GPort1

A

data from GPort 2

A

...

N

P

Start

ACK from

Slave

ACK from

Slave

No ACK

from Master

ACK from

Master

Reading from GPort 1

Slave Address

Register Address = 09h

Output to GPort 2

Output to GPort 3

At this moment, device

performs output to GPort 1

R/W

Stop

P

S

A6 A5 A4 A3 A2 A1 A0

0

A

0

0

0

0

1

0

0

1

A

data from GPort1

A

data from GPort 2

A

data from GPort 3

A

...

Start

ACK from

Slave

ACK from

Slave

ACK from

Slave

ACK from

Slave

Writing from GPort 1

Document Number: 38-12036 Rev. *B

Page 9 of 24

[+] Feedback

CYPRESS [ CYPRESS ]

CYPRESS [ CYPRESS ]