CS4365

Right Channel

LRCK

SCLK

Left Channel

SDINx

1 0

19 18 17 16

19 18 17 16

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

15 14 13 12 11 10

9 8 7 6 5 4 3 2 1 0

32 clocks

Figure 13. Format 4 - Right-Justified 20-bit Data

Right Channel

LRCK

SCLK

Left Channel

SDINx

1 0

17 16

17 16

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

15 14 13 12 11 10

9 8 7 6 5 4 3 2 1 0

32 clocks

Figure 14. Format 5 - Right-Justified 18-bit Data

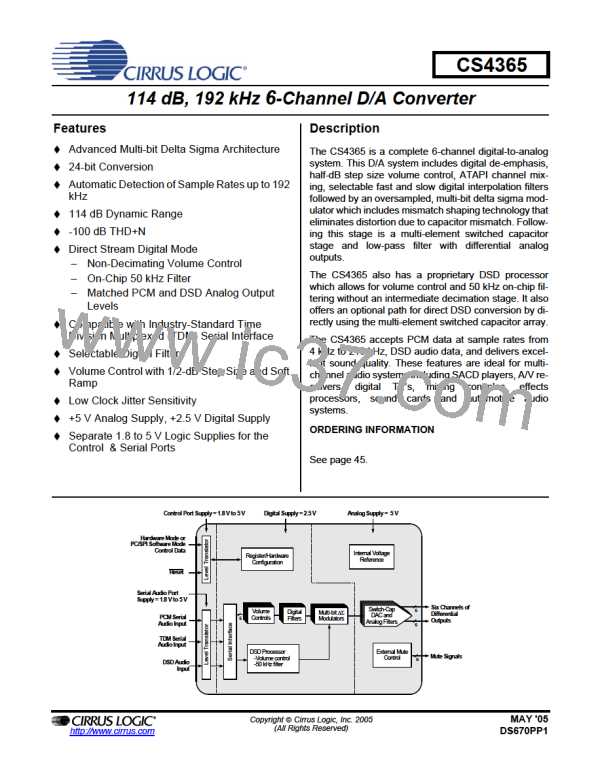

3.3.1 OLM #1

OLM #1 serial audio interface format operates in single, double, or quad-speed mode and

will slave to SCLK at 128 Fs. Six channels of MSB first 20-bit PCM data are input on

SDIN1.

64 clks

64 clks

LRCK

Left Channel

Right Channel

SCLK

MSB

LSB MSB

LSB MSB

DAC_A3

20 clks

LSB

MSB

DAC_B1

20 clks

LSB MSB

LSB MSB

LSB

DAC_B3

20 clks

MSB

SDIN1

DAC_A2

20 clks

DAC_B2

20 clks

DAC_A1

20 clks

Figure 15. Format 8 - One Line Mode 1

DS670PP1

23

CIRRUS [ CIRRUS LOGIC ]

CIRRUS [ CIRRUS LOGIC ]