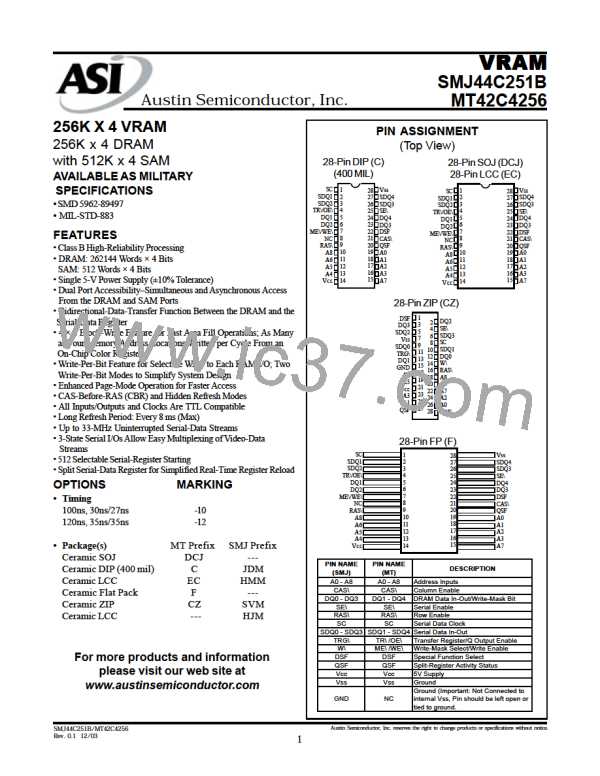

VRAM

SMJ44C251B

MT42C4256

Austin Semiconductor, Inc.

TIMING REQUIREMENTS (continued)1

-10

-12

PARAMETER

SYM/ALT. SYM MIN

MAX

MIN

MAX

UNIT

Setup time, SDQ before SC high

t

/t

0

0

ns

su(SDS) SDS

Hold time, column address after CAS\ low

Hold time, DSF after CAS\ low

t

/t

20

20

15

15

20

20

15

15

ns

ns

ns

ns

h(CLCA) CAH

t

/t

h(SFC) CFH

Hold time, row address after RAS\ low

t

/t

h(RA) RAH

Hold time, TRG\ after RAS\ low

t

/t

h(TRG) TLH

Hold time, SE\ after RAS\ low with

t

/t

15

15

ns

h(SE) REH

6

TRG\ = W\ = low

Hold time, write mask, transfer enable

after RAS\ low

Hold time, DQ after RAS\ low

(write-mask operation)

t

/t

15

15

15

15

ns

ns

h(RWM) RWH

t

/t

h(RDQ) MH

Hold time, DSF after RAS\ low

t

/t

15

45

20

45

20

0

15

45

25

50

25

0

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

h(SFR) RFH

7

t

/t

h(RLCA) AR

Hold time, column address after RAS\ low

Hold time, data after CAS\ low

t

/t

h(CLD) DH

7

t

/t

h(RLD) DHR

Hold time, data after RAS\ low

Hold time, data after W\ low

t

/t

h(WLD) DH

8

t

/t

h(CHrd) RCH

Hold time, read after CAS\ high

8

t

/t

10

30

50

25

5

10

35

55

30

5

h(RHrd) RRH

Hold time, read after RAS\ high

Hold time, write after CAS\ low

t

t

/t

h(CLW) WCH

7

/t

h(RLW) WCR

Hold time, write after RAS\ low

9

t

/t

h(WLG) OEH

Hold time, TRG\ after W\ low

Hold time, SDQ after SC high

Hold time, SDQ after SC high

Hold time, DSF after RAS\ low

Hold time, serial-write disable

Delay time, RAS\ low to CAS\ high

Delay time, CAS\ high to RAS\ low

Delay time, CAS\ low to RAS\ high

t

/t

h(SDS) SDH

t

/t

5

5

h(SHSQ) SOH

t

/t

45

20

100

0

45

20

120

0

h(RSF) FHR

t

/t

h(SCSE) SWIH

t

/t

d(RLCH) CSH

t

t

/t

d(CHRL) CRP

/t

25

55

25

50

130

85

25

10

10

30

65

25

60

155

100

25

10

10

d(CLRH) RSH

10,11

t

/t

d(CLWL) CWD

Delay time, CAS\ low to W\ low

12

t

/t

75

90

d(RLCL) RCD

Delay time, RAS\ low to CAS\ low

Delay time, column address to RAS\ high

t

/t

d(CARH) RAL

10

t

/t

d(RLWL) RWD

Delay time, RAS\ low to W\ low

10

t

/t

d(CAWL) AWD

Delay time, column address to W\ low

13

t

/t

d(RLCH)RF CHR

Delay time, RAS\ low to CAS\ high

13

t

/t

d(CLRL)RF CSR

Delay time, CAS\ low to RAS\ low

13

t

/t

d(RHCL)RF RPC

Delay time, RAS\ high to CAS\ low

Delay time, CAS\ low to TRG\ high for DRAM read

cycles

t

25

30

ns

d(CLGH)

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

SMJ44C251B/MT42C4256

Rev. 0.1 12/03

20

AUSTIN [ AUSTIN SEMICONDUCTOR ]

AUSTIN [ AUSTIN SEMICONDUCTOR ]