Idle Mode

When the SM2..0 bits are written to 000, the SLEEP instruction makes the MCU enter

Idle mode, stopping the CPU but allowing the SPI, USART, Analog Comparator, ADC,

2-wire Serial Interface, Timer/Counters, Watchdog, and the interrupt system to continue

operating. This sleep mode basically halts clkCPU and clkFLASH, while allowing the other

clocks to run.

Idle mode enables the MCU to wake up from external triggered interrupts as well as

internal ones like the Timer Overflow and USART Transmit Complete interrupts. If

wake-up from the Analog Comparator interrupt is not required, the Analog Comparator

can be powered down by setting the ACD bit in the Analog Comparator Control and Sta-

tus Register – ACSR. This will reduce power consumption in Idle mode. If the ADC is

enabled, a conversion starts automatically when this mode is entered.

ADC Noise Reduction

Mode

When the SM2..0 bits are written to 001, the SLEEP instruction makes the MCU enter

ADC Noise Reduction mode, stopping the CPU but allowing the ADC, the external

interrupts, the 2-wire Serial Interface address watch, Timer/Counter2, and the

Watchdog to continue operating (if enabled). This sleep mode basically halts clkI/O

clkCPU, and clkFLASH, while allowing the other clocks to run.

,

This improves the noise environment for the ADC, enabling higher resolution measure-

ments. If the ADC is enabled, a conversion starts automatically when this mode is

entered. Apart from the ADC Conversion Complete interrupt, only an External Reset, a

Watchdog System Reset, a Watchdog Interrupt, a Brown-out Reset, a 2-wire Serial

Interface address match, a Timer/Counter2 interrupt, an SPM/EEPROM ready interrupt,

an external level interrupt on INT0 or INT1 or a pin change interrupt can wake up the

MCU from ADC Noise Reduction mode.

Power-down Mode

When the SM2..0 bits are written to 010, the SLEEP instruction makes the MCU enter

Power-down mode. In this mode, the external Oscillator is stopped, while the external

interrupts, the 2-wire Serial Interface address watch, and the Watchdog continue operat-

ing (if enabled). Only an External Reset, a Watchdog System Reset, a Watchdog

Interrupt, a Brown-out Reset, a 2-wire Serial Interface address match, an external level

interrupt on INT0 or INT1, or a pin change interrupt can wake up the MCU. This sleep

mode basically halts all generated clocks, allowing operation of asynchronous modules

only.

Note that if a level triggered interrupt is used for wake-up from Power-down mode, the

changed level must be held for some time to wake up the MCU. Refer to “External Inter-

rupts” on page 80 for details.

When waking up from Power-down mode, there is a delay from the wake-up condition

occurs until the wake-up becomes effective. This allows the clock to restart and become

stable after having been stopped. The wake-up period is defined by the same CKSEL

Fuses that define the Reset Time-out period, as described in “Clock Sources” on page

25.

Power-save Mode

When the SM2..0 bits are written to 011, the SLEEP instruction makes the MCU enter

Power-save mode. This mode is identical to Power-down, with one exception:

If Timer/Counter2 is enabled, it will keep running during sleep. The device can wake up

from either Timer Overflow or Output Compare event from Timer/Counter2 if the corre-

sponding Timer/Counter2 interrupt enable bits are set in TIMSK2, and the Global

Interrupt Enable bit in SREG is set.

If Timer/Counter2 is not running, Power-down mode is recommended instead of Power-

save mode.

36

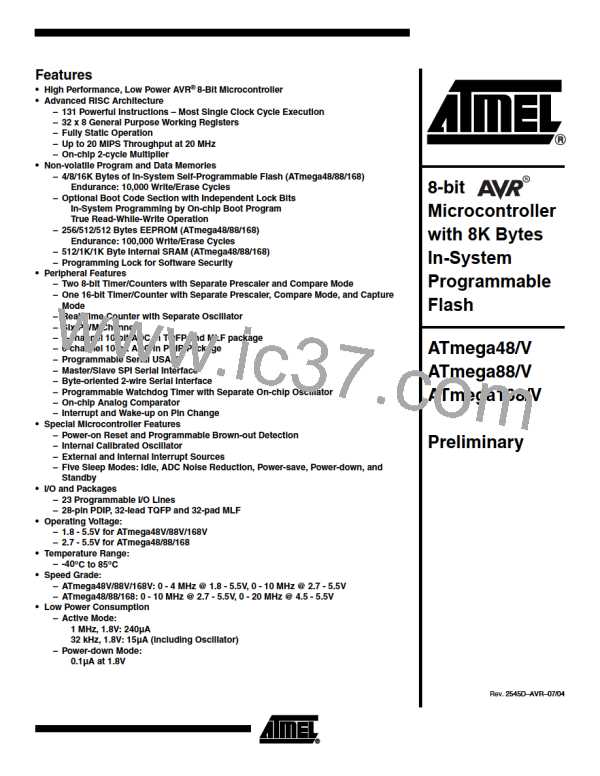

ATmega48/88/168

2545D–AVR–07/04

ATMEL [ ATMEL ]

ATMEL [ ATMEL ]