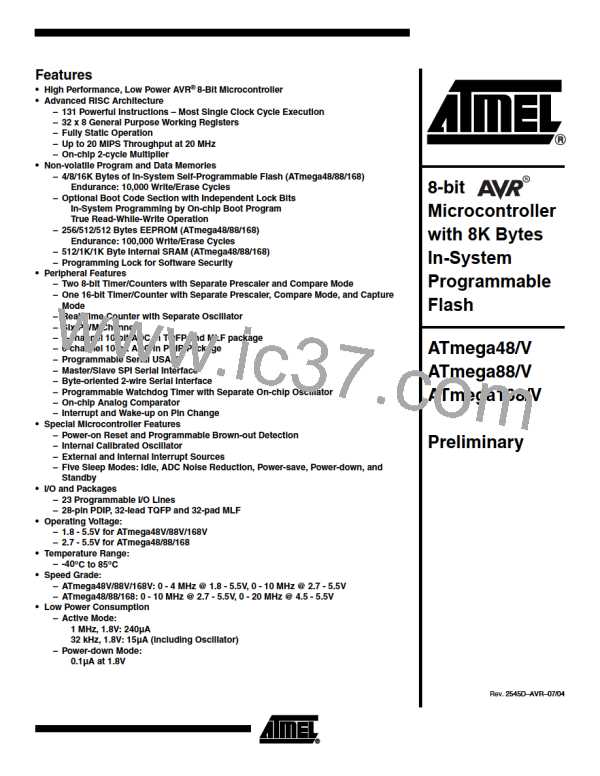

Figure 101. Analog to Digital Converter Block Schematic Operation

ADC CONVERSION

COMPLETE IRQ

8-BIT DATA BUS

15

0

ADC MULTIPLEXER

SELECT (ADMUX)

ADC DATA REGISTER

(ADCH/ADCL)

ADC CTRL. & STATUS

REGISTER (ADCSRA)

MUX DECODER

PRESCALER

CONVERSION LOGIC

AVCC

INTERNAL 1.1V

REFERENCE

SAMPLE & HOLD

COMPARATOR

AREF

GND

10-BIT DAC

-

+

BANDGAP

REFERENCE

ADC7

ADC6

ADC5

ADC4

ADC3

ADC2

ADC1

ADC0

ADC MULTIPLEXER

OUTPUT

INPUT

MUX

The ADC converts an analog input voltage to a 10-bit digital value through successive

approximation. The minimum value represents GND and the maximum value represents

the voltage on the AREF pin minus 1 LSB. Optionally, AVCC or an internal 1.1V refer-

ence voltage may be connected to the AREF pin by writing to the REFSn bits in the

ADMUX Register. The internal voltage reference may thus be decoupled by an external

capacitor at the AREF pin to improve noise immunity.

The analog input channel is selected by writing to the MUX bits in ADMUX. Any of the

ADC input pins, as well as GND and a fixed bandgap voltage reference, can be selected

as single ended inputs to the ADC. The ADC is enabled by setting the ADC Enable bit,

ADEN in ADCSRA. Voltage reference and input channel selections will not go into effect

until ADEN is set. The ADC does not consume power when ADEN is cleared, so it is

recommended to switch off the ADC before entering power saving sleep modes.

The ADC generates a 10-bit result which is presented in the ADC Data Registers,

ADCH and ADCL. By default, the result is presented right adjusted, but can optionally

be presented left adjusted by setting the ADLAR bit in ADMUX.

232

ATmega48/88/168

2545D–AVR–07/04

ATMEL [ ATMEL ]

ATMEL [ ATMEL ]