Assembly Code Example(1)

USART_Init:

clr r18

out UBRRnH,r18

out UBRRnL,r18

; Setting the XCKn port pin as output, enables master mode.

sbi XCKn_DDR, XCKn

; Set MSPI mode of operation and SPI data mode 0.

ldi r18, (1<<UMSELn1)|(1<<UMSELn0)|(0<<UCPHAn)|(0<<UCPOLn)

out UCSRnC,r18

; Enable receiver and transmitter.

ldi r18, (1<<RXENn)|(1<<TXENn)

out UCSRnB,r18

; Set baud rate.

; IMPORTANT: The Baud Rate must be set after the transmitter is

enabled!

out UBRRnH, r17

out UBRRnL, r18

ret

C Code Example(1)

void USART_Init( unsigned int baud )

{

UBRRn = 0;

/* Setting the XCKn port pin as output, enables master mode. */

XCKn_DDR |= (1<<XCKn);

/* Set MSPI mode of operation and SPI data mode 0. */

UCSRnC = (1<<UMSELn1)|(1<<UMSELn0)|(0<<UCPHAn)|(0<<UCPOLn);

/* Enable receiver and transmitter. */

UCSRnB = (1<<RXENn)|(1<<TXENn);

/* Set baud rate. */

/* IMPORTANT: The Baud Rate must be set after the transmitter is

enabled */

UBRRn = baud;

}

Note:

1. The example code assumes that the part specific header file is included. For I/O Reg-

isters located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI"

instructions must be replaced with instructions that allow access to extended I/O. Typ-

ically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

Data Transfer

Using the USART in MSPI mode requires the Transmitter to be enabled, i.e. the TXENn

bit in the UCSRnB register is set to one. When the Transmitter is enabled, the normal

port operation of the TxDn pin is overridden and given the function as the Transmitter's

serial output. Enabling the receiver is optional and is done by setting the RXENn bit in

the UCSRnB register to one. When the receiver is enabled, the normal pin operation of

the RxDn pin is overridden and given the function as the Receiver's serial input. The

XCKn will in both cases be used as the transfer clock.

192

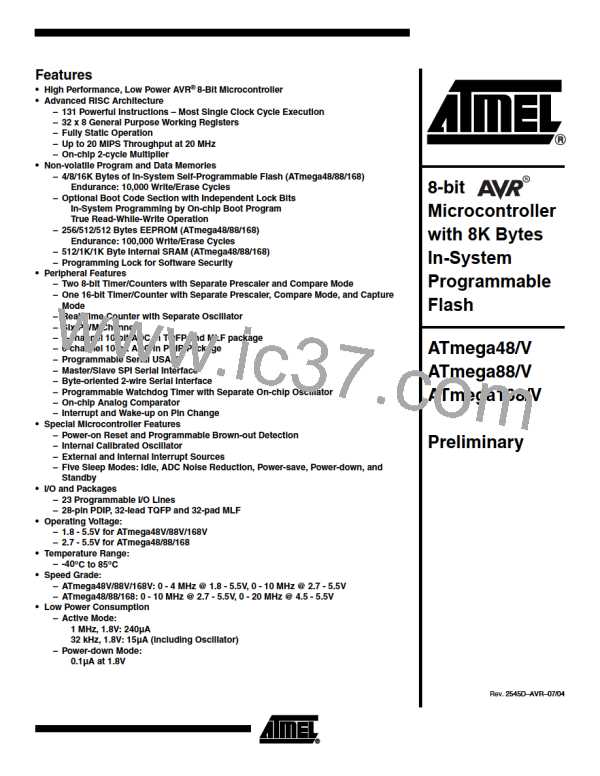

ATmega48/88/168

2545D–AVR–07/04

ATMEL [ ATMEL ]

ATMEL [ ATMEL ]