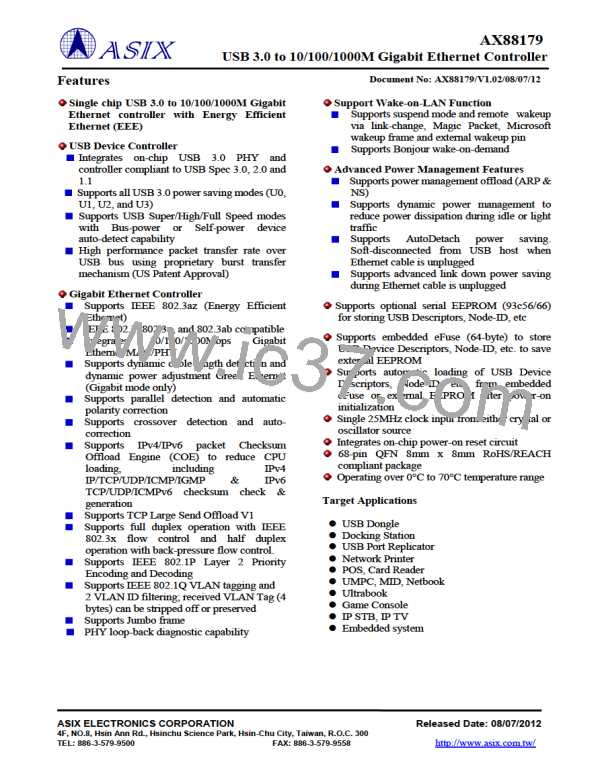

AX88179

USB 3.0 to 10/100/1000M Gigabit Ethernet Controller

3.4 GMAC Core

The MAC core supports IEEE 802.3, IEEE 802.3u and IEEE 802.3ab MAC sub-layer functions, such as basic MAC frame

receive and transmit, CRC checking and generation, filtering, forwarding, flow-control in full-duplex mode, and

collision-detection and handling in half-duplex mode, etc. It supports virtual local area network (VLAN)-tagged frames

according to IEEE 802.1Q specification in both transmit and receive functions, CRC-32 checking at full speed using a

multi-stage, cyclic redundancy code (CRC) calculation architecture with optional forwarding of the frame check sequence

(FCS) field to the user application CRC-32 generation and append on transmit.

3.5 Checksum Offload Engine (COE)

The Checksum Offload Engine (COE) supports IPv4, IPv6, layer 4 (TCP, UDP, ICMP, ICMPv6 and IGMP) header

processing functions and real time checksum calculation in hardware

The COE supports the following features in layer 3:

IP header parsing, including IPv4 and IPv6

IPv6 routing header type 0 supported

IPv4 header checksum check and generation (There is no checksum field in IPv6 header)

Detecting on RX direction for IP packets with error header checksum

The COE supports the following features in layer 4:

TCP and UDP checksum check and generation for non-fragmented packet

TCP Large Send Offload V1

ICMP, ICMPv6 and IGMP message checksum check and generation for non-fragmented packet

3.6 Memory Arbiter

The memory arbiter block is responsible for storing received MAC frames into on-chip SRAM (packet buffer) and then

forwarding it to the USB bus upon request from the USB host via Bulk IN transfer. It also monitors the packet buffer usage

in full-duplex mode for triggering PAUSE frame (or in half-duplex mode to activate Backpressure jam signal) transmission

out on transmit (TX) direction. The memory arbiter block is also responsible for storing MAC frames received from the

USB host via Bulk OUT transfer and scheduling transmission out towards Ethernet network.

13

Copyright © 2011-2012 ASIX Electronics Corporation. All rights reserved.

ASIX [ ASIX ELECTRONICS CORPORATION ]

ASIX [ ASIX ELECTRONICS CORPORATION ]